# **HW/SW Co-designed Processors:** Challenges, Design Choices and a Simulation Infrastructure for Evaluation

José Cano<sup>1</sup>, Rakesh Kumar<sup>2</sup>, Aleksandar Brankovic<sup>3</sup>, Demos Pavlou<sup>4</sup>, Kyriakos Stavrou<sup>4</sup>, Enric Gibert<sup>5</sup>, Alejandro Martínez<sup>6</sup>, Antonio González<sup>7</sup>

<sup>1</sup>University of Edinburgh, UK <sup>2</sup>Uppsala University, Sweden <sup>3</sup>Intel <sup>4</sup>11pets <sup>5</sup>Pharmacelera <sup>6</sup>ARM <sup>7</sup>Universitat Politècnica de Catalunya, Spain

### The problem

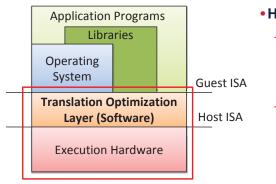

HW/SW co-designed processor

- HW/SW co-designed processors

- -Lot of potential to improve

- Performance (DBTO in SW)

Energy efficiency (simple HW)

- -Some projects from industry

- IBM DAISY/BOA, Transmeta Crusoe/Efficeon, NVIDIA Denver

- But no successful product yet

-No major project from academia

- These processors need to address some **key challenges** before they can become mainstream

- There are **no simulation infrastructures** for evaluating different **design choices** and **trade-offs** to meet these challenges

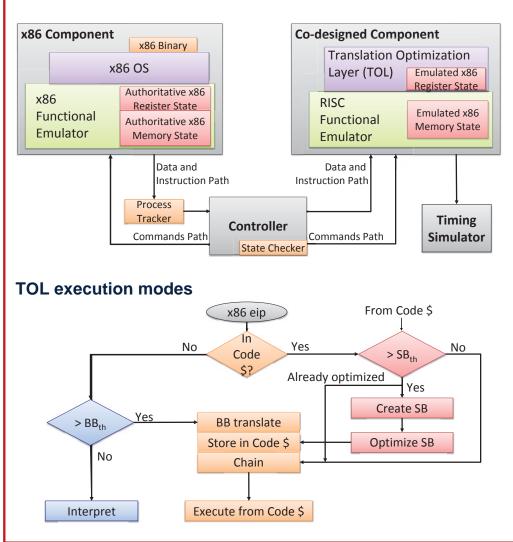

## **DARCO: Simulation infrastructure**

## **Challenges and design choices**

- Where to implement (HW or SW) microarchitectural features

Instruction decoding/reordering, register renaming, memory disambiguation, ...

- How to reduce "startup delay"

- One of the major problems of Transmeta processors

- When and where to translate/optimize the guest binaries

As soon as code becomes "hot"?

- How to address speculative execution (memory, control)

Checkpointing granularity?

- When and how to profile the execution

Overhead vs opportunity for improvement

## Challenges in building an infrastructure vs DARCO

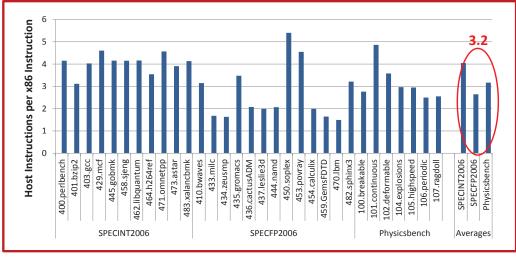

#### **DARCO: Evaluation**

#### Conclusions

#### HW/SW co-designed processors

- Potential to improve energy efficiency and performance

- Several industrial projects, no major project in academia

#### • Challenges

- To become mainstream (e.g. startup delay)

- To build a simulation infrastructure (e.g. software layer overhead)

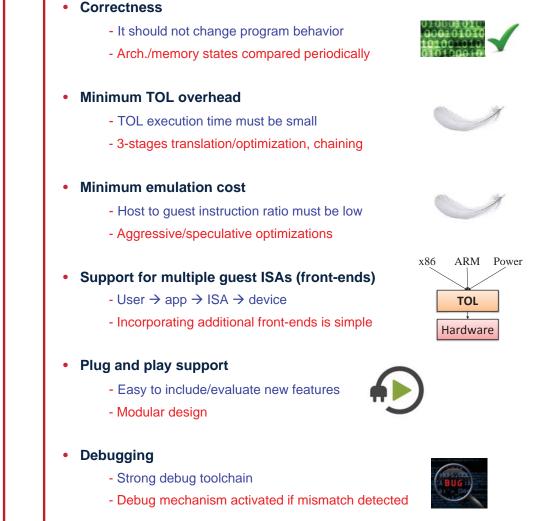

#### • DARCO

- May enable academic research in HW/SW co-designed domain

- Modular infrastructure, easy to add new components/optimizations

ARM Research Summit, Cambridge, UK - September 11-13, 2017

Institute for Computing Systems Architecture