# ARCHITECTURE AWARE PARALLEL PROGRAMMING IN GLASGOW PARALLEL HASKELL (GPH)

By

Mustafa KH. Aswad

Submitted for the Degree of

Doctor of Philosophy

at Heriot-Watt University

on Completion of Research in the

School of Mathematical and Computer Sciences

August, 2012

The copyright in this thesis is owned by the author. Any quotation from the thesis or use of any of the information contained in it must acknowledge this thesis as the source of the quotation or information.

| I hereby declare that the work presented in this the-    |

|----------------------------------------------------------|

| sis was carried out by myself at Heriot-Watt University, |

| Edinburgh, except where due acknowledgement is made,     |

| and has not been submitted for any other degree.         |

Mustafa Kh. Aswad (Candidate)

Phil Trinder, Hans-Wolfgang Loidl (Supervisors)

(Date)

#### Abstract

General purpose computing architectures are evolving quickly to become many-core and hierarchical: i.e. a core can communicate more quickly locally than globally. To be effective on such architectures, programming models must be aware of the communications hierarchy. This thesis investigates a programming model that aims to share the responsibility of task placement, load balance, thread creation, and synchronisation between the application developer and the runtime system.

The main contribution of this thesis is the development of four new architecture-aware constructs for Glasgow parallel Haskell that exploit information about task size and aim to reduce communication for small tasks, preserve data locality, or to distribute large units of work. We define a semantics for the constructs that specifies the sets of PEs that each construct identifies, and we check four properties of the semantics using QuickCheck.

We report a preliminary investigation of architecture aware programming models that abstract over the new constructs. In particular, we propose architecture aware evaluation strategies and skeletons. We investigate three common paradigms, such as data parallelism, divide-and-conquer and nested parallelism, on hierarchical architectures with up to 224 cores. The results show that the architecture-aware programming model consistently delivers better speedup and scalability than existing constructs, together with a dramatic reduction in the execution time variability.

We present a comparison of functional multicore technologies and it reports some of the first ever multicore results for the Feedback Directed Implicit Parallelism (FDIP) and the semi-explicit parallelism (GpH and Eden) languages. The comparison reflects the growing maturity of the field by systematically evaluating four parallel Haskell implementations on a common multicore architecture. The comparison contrasts the programming effort each language requires with the parallel performance delivered.

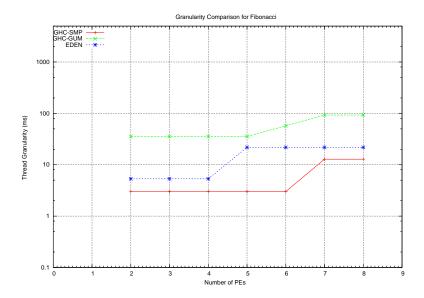

We investigate the minimum thread granularity required to achieve satisfactory performance for three implementations parallel functional language on a multicore platform. The results show that GHC-GUM requires a larger thread granularity than Eden and GHC-SMP. The thread granularity rises as the number of cores rises.

## Acknowledgements

My praises to God for giving me the good health, the strength of determination and support to finish my work successfully.

I would like to thank my PhD supervisor, Professor Phil Trinder, for all his enthusiasm, guidance and support over the years. He was a constant source of inspiration and I have benefited greatly from his experience and wisdom. I would also like to thank the various second supervisors I have been lucky enough to work with over the course of this PhD, particularly Dr Hans Wolfgang Loidl who was invaluable in providing guidance from a different perspective.

Many thanks to the Libyan higher education sector for offering me this scholarship. And also I would like to thank them for providing the finance support throughout the years of study for me and my family.

Last, but by no means least, I wish to thank my family for their love and affection.

| 1        | Intr | oduct  | ion                                       | 1  |

|----------|------|--------|-------------------------------------------|----|

|          | 1.1  | Thesis | s Statement                               | 3  |

|          | 1.2  | Contr  | ibutions                                  | 4  |

|          | 1.3  | Thesis | s Structure                               | 6  |

|          | 1.4  | Autho  | orship and Publications                   | 7  |

| <b>2</b> | Bac  | kgrou  | $\mathbf{nd}$                             | 10 |

|          | 2.1  | Parall | el Hardware                               | 10 |

|          |      | 2.1.1  | Classification by Memory Structure        | 11 |

|          |      | 2.1.2  | Multi-core Architecture                   | 12 |

|          |      | 2.1.3  | Homogeneous vs Heterogeneous Multicore    | 13 |

|          |      | 2.1.4  | Distributed Computing                     | 14 |

|          |      | 2.1.5  | Summary                                   | 17 |

|          | 2.2  | Parall | el Programming Classifications            | 19 |

|          |      | 2.2.1  | Parallel Software Development             | 20 |

|          |      | 2.2.2  | Parallel Programming Models and Languages | 22 |

|   |                 | 2.2.3                                                | Implicit Models                          | 25                                                                          |

|---|-----------------|------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------|

|   |                 | 2.2.4                                                | Semi-Explicit Parallel Models            | 27                                                                          |

|   |                 | 2.2.5                                                | Explicit Models                          | 36                                                                          |

|   |                 | 2.2.6                                                | Hybrid Programming Models                | 38                                                                          |

|   |                 | 2.2.7                                                | Summary                                  | 39                                                                          |

|   | 2.3             | Key R                                                | Cuntime Aspects in a Semi-Explicit Model | 42                                                                          |

|   |                 | 2.3.1                                                | Thread Creation and Synchronisation      | 42                                                                          |

|   |                 | 2.3.2                                                | Storage Management                       | 45                                                                          |

|   |                 | 2.3.3                                                | Data Locality                            | 46                                                                          |

|   | 2.4             | Summ                                                 | ary                                      | 48                                                                          |

|   |                 |                                                      |                                          |                                                                             |

| 3 | Mu              | lticore                                              | Parallel Haskell Comparison              | 50                                                                          |

| 3 | <b>Mu</b> : 3.1 |                                                      | Parallel Haskell Comparison              | <b>50</b>                                                                   |

| 3 |                 |                                                      | -                                        |                                                                             |

| 3 |                 | Introd                                               | luction                                  | 50                                                                          |

| 3 | 3.1             | Introd                                               | BenchMark Suite                          | 50<br>53                                                                    |

| 3 | 3.1             | Introd 3.1.1 Parall                                  | BenchMark Suite                          | 50<br>53<br>54                                                              |

| 3 | 3.1             | Introd 3.1.1 Parall 3.2.1                            | BenchMark Suite                          | 50<br>53<br>54<br>55                                                        |

| 3 | 3.1             | Introd<br>3.1.1<br>Parall<br>3.2.1<br>3.2.2<br>3.2.3 | BenchMark Suite                          | 50<br>53<br>54<br>55<br>57                                                  |

| 3 | 3.1             | Introd<br>3.1.1<br>Parall<br>3.2.1<br>3.2.2<br>3.2.3 | BenchMark Suite                          | <ul><li>50</li><li>53</li><li>54</li><li>55</li><li>57</li><li>61</li></ul> |

| 3 | 3.1             | 3.1.1 Parall 3.2.1 3.2.2 3.2.3 Parall                | BenchMark Suite                          | 500<br>533<br>544<br>555<br>577<br>611                                      |

|   |     | 3.3.4   | Eden Implementation                        | 69  |

|---|-----|---------|--------------------------------------------|-----|

|   |     | 3.3.5   | Implementation Comparison                  | 70  |

|   | 3.4 | Exper   | iment Design                               | 72  |

|   |     | 3.4.1   | Measurement Methodology                    | 72  |

|   | 3.5 | Runtin  | me Comparison                              | 74  |

|   | 3.6 | Progr   | ramming Effort and Performance Results     | 80  |

|   |     | 3.6.1   | FDIP Multicore Performance                 | 81  |

|   |     | 3.6.2   | GpH-SMP Multicore Performance              | 82  |

|   |     | 3.6.3   | GpH-GUM Multicore Performance              | 83  |

|   |     | 3.6.4   | Eden Multicore Performance                 | 84  |

|   | 3.7 | Comp    | arative Study                              | 85  |

|   |     | 3.7.1   | Programming Effort Comparison              | 85  |

|   |     | 3.7.2   | Scalability                                | 87  |

|   |     | 3.7.3   | Performance Comparison                     | 88  |

|   | 3.8 | Conclu  | ısion                                      | 90  |

|   |     | 3.8.1   | Summary                                    | 90  |

|   |     | 3.8.2   | Discussion                                 | 92  |

| 4 | Par | allel P | rogramming Practice                        | 96  |

|   | 4.1 | Using   | and benchmarking New Evaluation Strategies | 97  |

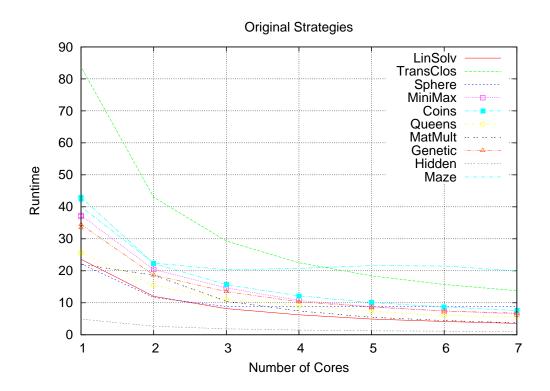

|   |     | 4.1.1   | Original Strategies                        | 97  |

|   |     | 4.1.2   | Space Leak Problem                         | 101 |

|   |     | 4.1.3   | New Eva    | duation Strategies                 | 104 |

|---|-----|---------|------------|------------------------------------|-----|

|   |     | 4.1.4   | Using St   | rategies for Parallel Paradigms    | 107 |

|   |     |         | 4.1.4.1    | Task Parallelism                   | 107 |

|   |     |         | 4.1.4.2    | Data-oriented Parallelism          | 110 |

|   |     | 4.1.5   | Evaluati   | on of the New Strategies           | 112 |

|   |     |         | 4.1.5.1    | Apparatus                          | 112 |

|   |     |         | 4.1.5.2    | Sequential Overhead                | 115 |

|   |     |         | 4.1.5.3    | Parallel Performance of Strategies | 116 |

|   | 4.2 | Granu   | larity Cor | ntrol                              | 119 |

|   |     | 4.2.1   | The Imp    | ortance of Thread Granularity      | 119 |

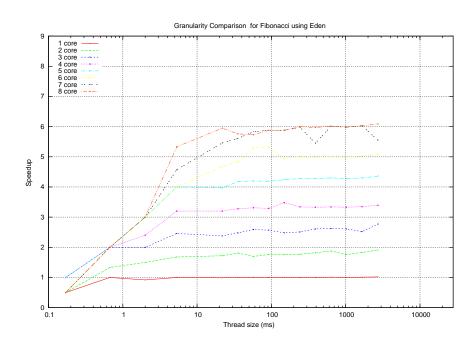

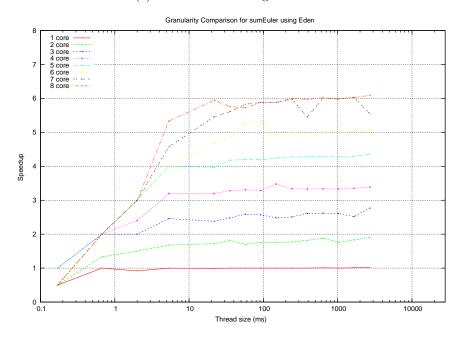

|   |     | 4.2.2   | Eden Mu    | ulticore Thread Granularity        | 121 |

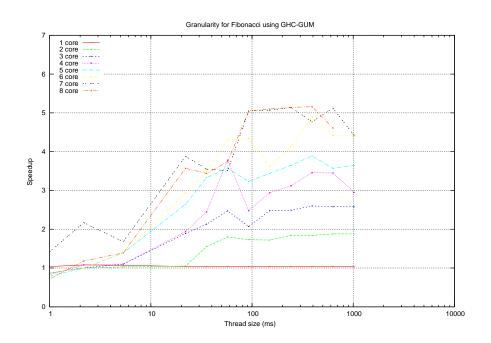

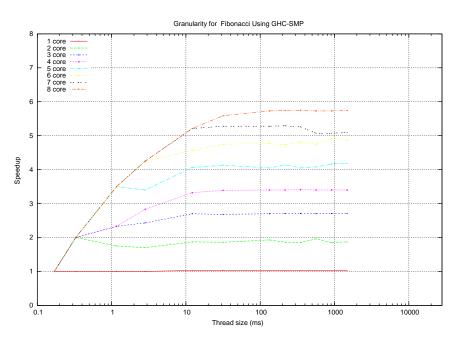

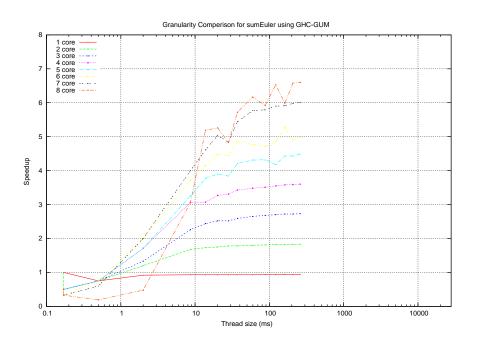

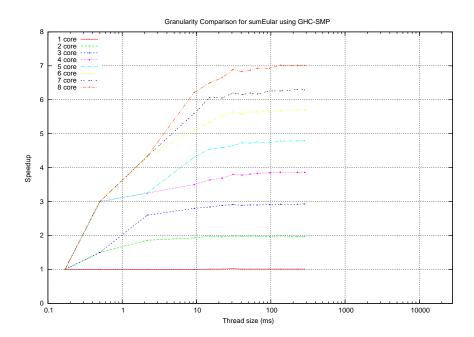

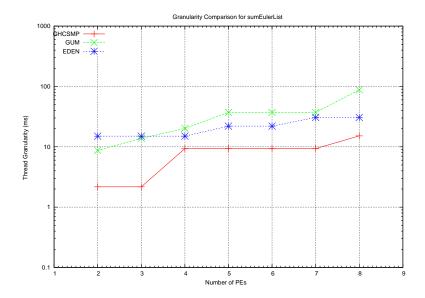

|   |     | 4.2.3   | Thread (   | Granularity of Parallel Haskells   | 122 |

|   |     | 4.2.4   | Discussio  | on                                 | 130 |

|   | 4.3 | Summ    | ary        |                                    | 132 |

| 5 | Arc | hitectı | are-Awar   | re Constructs                      | 133 |

|   | 5.1 | The T   | rend Towa  | ards Hierarchical Architectures    | 135 |

|   | 5.2 | Other   | Architect  | ure-Aware Languages                | 136 |

|   | 5.3 | New A   | Architectu | re-Aware Constructs                | 138 |

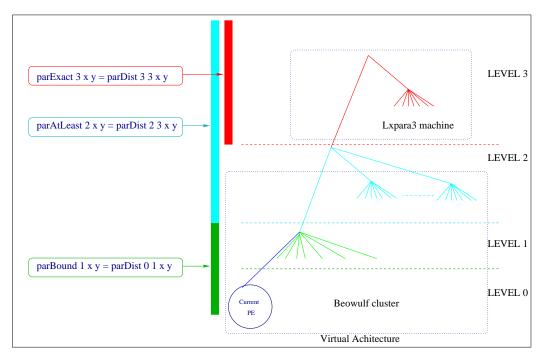

|   |     | 5.3.1   | Virtual A  | Architectures                      | 138 |

|   |     | 5.3.2   | Placing '  | Task on Hierarchical Architecture  | 139 |

|   |     | 5.3.3   | New Cor    | nstructs                           | 142 |

| 5.4 | The S | emantics of Constructs                     |

|-----|-------|--------------------------------------------|

|     | 5.4.1 | Distance Function                          |

|     | 5.4.2 | setparDist Function                        |

|     | 5.4.3 | setparBound Function                       |

|     | 5.4.4 | setparAtLeast Function                     |

|     | 5.4.5 | Construct Properties Test                  |

|     |       | 5.4.5.1 Basic Properties                   |

|     |       | 5.4.5.2 Specialised Properties             |

|     | 5.4.6 | Summary                                    |

| 5.5 | Imple | mentation of Architecture-Aware Constructs |

|     | 5.5.1 | Runtime Systems Modification               |

|     | 5.5.2 | Work Placement Mechanism                   |

|     | 5.5.3 | parDist Primitive Implementation           |

| 5.6 | Archi | tecture-Aware Constructs Evaluation        |

|     | 5.6.1 | Divide-and-Conquer Parallelism             |

|     | 5.6.2 | Data Parallelism                           |

|     | 5.6.3 | Nested Parallelism                         |

|     | 5.6.4 | Performance Variability                    |

|     | 5.6.5 | Discussion                                 |

| 5.7 | Apply | ing constructs in other Languages          |

| 5.8 | Summ  | 9ry 170                                    |

| 6 | Tow | vards A | Architecture Aware Programming Models       | 182 |

|---|-----|---------|---------------------------------------------|-----|

|   | 6.1 | Archit  | secture-Aware Decisions                     | 183 |

|   | 6.2 | Archit  | secture Aware Evaluation Strategies         | 186 |

|   |     | 6.2.1   | Using the parDistList Function              | 187 |

|   |     | 6.2.2   | Using the parListLevel Function             | 188 |

|   | 6.3 | Archit  | secture Aware Skeletons                     | 189 |

|   |     | 6.3.1   | An Architecture Aware Parallel Map Skeleton | 190 |

|   |     | 6.3.2   | A Divide-and-Conquer(DC) Skeleton           | 191 |

|   | 6.4 | Evalua  | ation of Architecture Aware Strategies      | 192 |

|   |     | 6.4.1   | SumEulerDist                                | 193 |

|   |     |         | 6.4.1.1 parListLevel Strategy Results       | 193 |

|   |     |         | 6.4.1.2 Deep Strategy Results               | 197 |

|   |     |         | 6.4.1.3 Summary:                            | 198 |

|   |     | 6.4.2   | Queen                                       | 199 |

|   |     |         | 6.4.2.1 Shared Memory Results               | 199 |

|   |     |         | 6.4.2.2 Distributed Memory Results          | 200 |

|   |     |         | 6.4.2.3 Architecture Awareness Comparison   | 202 |

|   |     |         | 6.4.2.4 Summary:                            | 205 |

|   | 6.5 | Evalua  | ation of the Architecture Aware Skeletons   | 206 |

|   |     | 6.5.1   | sumEulerSkel Results                        | 206 |

|   |     | 6.5.2   | Coins Results                               | 211 |

|   | 6.6 | Memo    | ry and Potential Parallelism Performance    | 214 |

|              | 6.7   | Summary                                          | 216 |

|--------------|-------|--------------------------------------------------|-----|

| 7            | Con   | nclusion                                         | 218 |

|              | 7.1   | Achievements and Contributions                   | 218 |

|              |       | 7.1.1 Architecture-aware Constructs              | 219 |

|              |       | 7.1.2 Programming and Performance Comparison:    | 221 |

|              | 7.2   | Limitations and Future Work                      | 222 |

| $\mathbf{A}$ | Ben   | chmark Code                                      | 225 |

|              | A.1   | parMapList Program                               | 225 |

|              | A.2   | parMapIntervals Program                          | 228 |

| В            | Loca  | ation Semantics of Architecture-Aware Constructs | 229 |

| $\mathbf{C}$ | Arc   | hitecture-Aware Programs                         | 236 |

|              | C.1   | sumEulerDist Code                                | 236 |

|              | C.2   | sumEulerSkel Program                             | 238 |

|              | C.3   | Coins Program                                    | 240 |

| Bi           | bliog | graphy                                           | 242 |

## List of Tables

| 1  | Memory Classification                                          | 18  |

|----|----------------------------------------------------------------|-----|

| 2  | Classification of Parallel Models                              | 25  |

| 3  | Comparison of some Popular Parallel Programming Languages      | 40  |

| 4  | Language-level Comparison of Parallel Haskells                 | 61  |

| 5  | Implementation-level Comparison of Parallel Haskells           | 70  |

| 6  | Sequential Runtime Comparison (seconds)                        | 74  |

| 7  | 8 Core Parallel Runtime Comparison (seconds)                   | 76  |

| 8  | FDIP Programs Improved                                         | 81  |

| 9  | GpH-SMP Programs Improved                                      | 82  |

| 10 | GpH-GUM Programs Improved                                      | 83  |

| 11 | Eden Programs Improved                                         | 84  |

| 12 | Comparative Multicore Performance Summary                      | 85  |

| 13 | Comparative Speedup of Parallel Haskells on Multi-core Machine | 90  |

| 14 | Programs Characteristics                                       | 113 |

| 15 | Sequential Runtime Overheads                                      | 115 |

|----|-------------------------------------------------------------------|-----|

| 16 | Speedups, Number of Sparks and Heap Consumption on 7 Cores.       | 119 |

| 17 | The Most Profitable Thread Granularities for the nfibList Program | 126 |

| 18 | The Most Profitable Thread Granularity of the sumEulerList Pro-   |     |

|    | gram                                                              | 127 |

| 19 | GpH par Construct Comparison (Increasingly Specific)              | 145 |

| 20 | A Static Information Table for Five Cores from Figure 34          | 159 |

| 21 | findLevel Configuration                                           | 163 |

| 22 | Task Size and Irregularity                                        | 165 |

| 23 | Variability of benchmark runtimes (11 executions) on 64 cores     | 176 |

| 24 | Comparison of parList and parListLevel (sumEulerDist)             | 195 |

| 25 | Comparison of parListLevel vs Deep                                | 197 |

| 26 | Runtime Comparison on Shared Memory (Queen)                       | 199 |

| 27 | Runtime Comparison on Distributed Memory (Queen)                  | 202 |

| 28 | Comparison of Divide-and-Conquer Skeleton (sumEulerSkel)          | 210 |

| 29 | Comparison of Divide-and-Conquer Skeleton (Coins)                 | 211 |

| 30 | Speedups, Number of Sparks and Memory Consumption on 16 cores:    | 215 |

# List of Figures

| 1  | Comparison of Single Core and Different Multicore Architectures $([2])$ | 12 |

|----|-------------------------------------------------------------------------|----|

| 2  | Hierarchical Architectures                                              | 17 |

| 3  | Types of the basic coordination constructs in GpH                       | 30 |

| 4  | Basic Coordination Constructs in Eden                                   | 33 |

| 5  | Sequential Top-level Boyer function                                     | 55 |

| 6  | Evaluation Strategies                                                   | 56 |

| 7  | GpH Top-level Boyer function                                            | 57 |

| 8  | Eden Farm Skeleton                                                      | 58 |

| 9  | Eden Master-Worker Skeleton (Static Task Pool)                          | 59 |

| 10 | Eden Top-level Boyer function                                           | 60 |

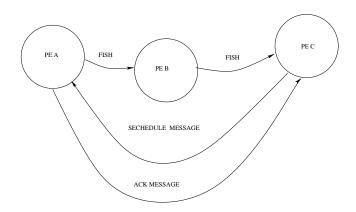

| 11 | GUM FISH - SCHEDULE - ACK Sequence                                      | 68 |

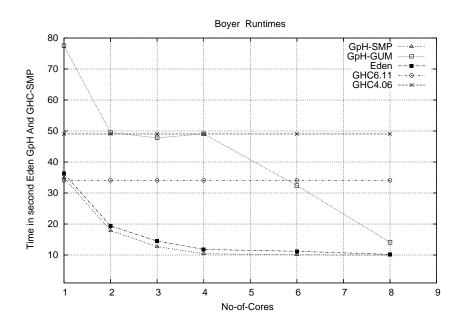

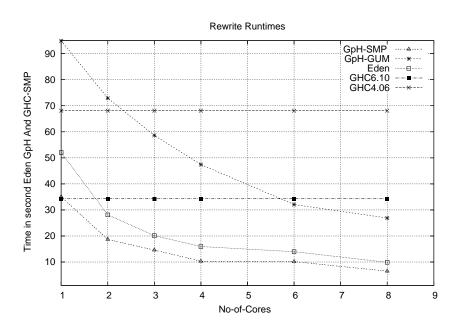

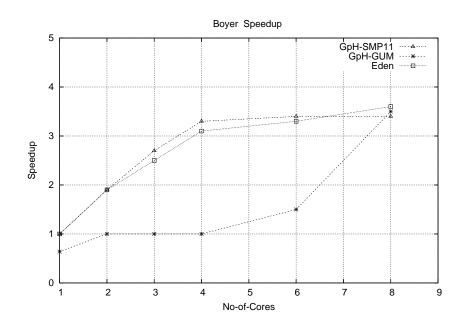

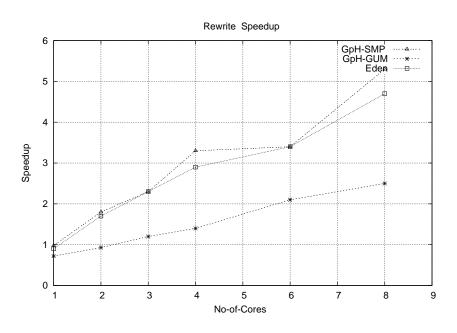

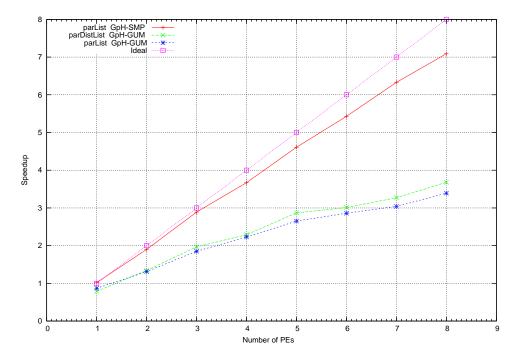

| 12 | Runtime Comparison of Parallel Haskells (Boyer/Rewrite)                 | 77 |

| 13 | Absolute Speedup Comparison of Parallel Haskells (Boyer/Rewrite)        | 78 |

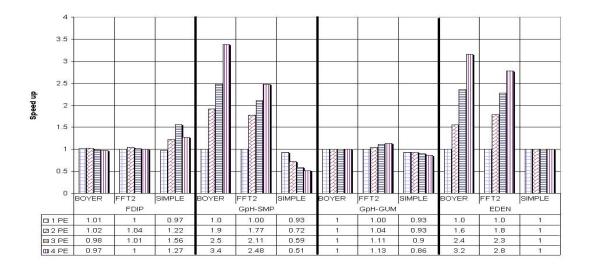

| 14 | Comparing the Performance Scalability of Parallel Haskells on 4         |    |

|    | Cores                                                                   | 87 |

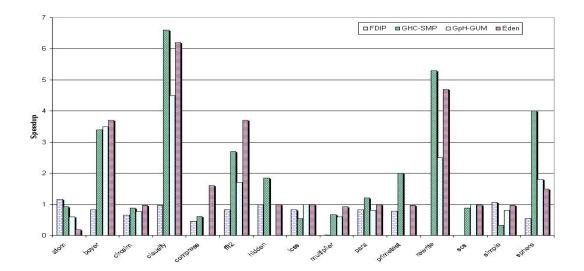

| 15 | Performance Comparison of Parallel Haskells (8 cores)         | 89  |

|----|---------------------------------------------------------------|-----|

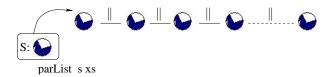

| 16 | parList Strategy                                              | 100 |

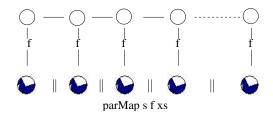

| 17 | parMap Strategy                                               | 101 |

| 18 | Original Strategies versus New Strategies                     | 107 |

| 19 | Coins Using Original Strategy                                 | 108 |

| 20 | Coins Using New Strategy                                      | 108 |

| 21 | Divide-and-Conquer Skeleton                                   | 110 |

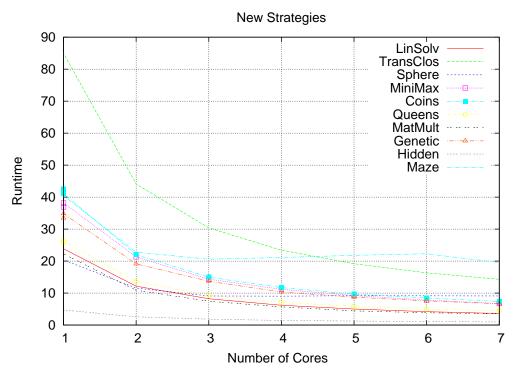

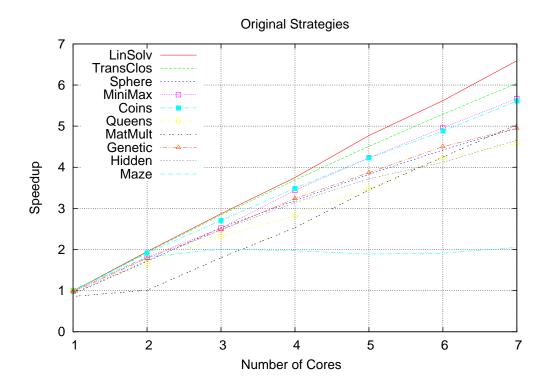

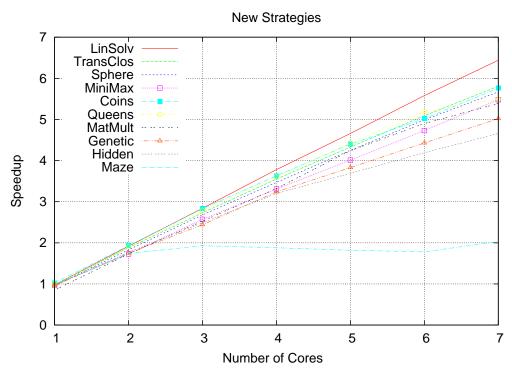

| 22 | Runtime Comparison of the Original and the New Strategies     | 117 |

| 23 | Speedups Comparison of the Original and the New Strategies    | 118 |

| 24 | nfibList Program                                              | 120 |

| 25 | Thread Granularity vs Speedup Comparison of nfibList          | 123 |

| 26 | Thread Granularity vs Speedup Comparison of nfibList          | 124 |

| 27 | The Most Profitable Thread Granularity Comparison of nfibList |     |

|    | Program                                                       | 125 |

| 28 | sumEulerList Program                                          | 126 |

| 29 | Thread Granularity vs Speedup Comparison of GpH-GUM and       |     |

|    | Eden Implementations of sumEulerList Program                  | 128 |

| 30 | Thread Granularity vs Speedup Comparison of GpH-SMP Imple-    |     |

|    | mentation of sumEulerList program                             | 129 |

| 31 | The Most Protable Thread Granularity of sumEulerList program  | 130 |

| 32 | Real and Virtual Hierarchical Architectures                   | 136 |

| 33 | New Architecture Aware Constructs                 |

|----|---------------------------------------------------|

| 34 | Using New Architecture Aware Constructs           |

| 35 | Architecture Aware Construct Definitions          |

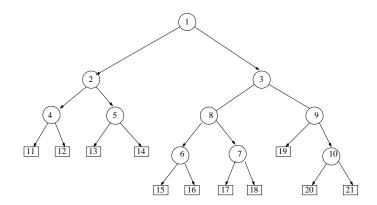

| 36 | An Example of Hierarchical Architecture           |

| 37 | Distance Function                                 |

| 38 | setparDist Locations Function                     |

| 39 | setparBound Locations Function                    |

| 40 | setparAtLeast Locations Function                  |

| 41 | Tree Example of Specialised Proposed Property One |

| 42 | Tree Example of Specialised Proposed Property Two |

| 43 | The original GUM Work Placement Mechanism         |

| 44 | Extended GUM Work Placement Mechanism             |

| 45 | parFibDist Program                                |

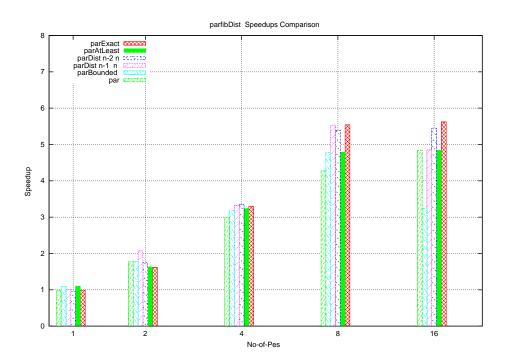

| 46 | parFibDist Speedup 164                            |

| 47 | parMapList Program                                |

| 48 | parMapIntervals Program                           |

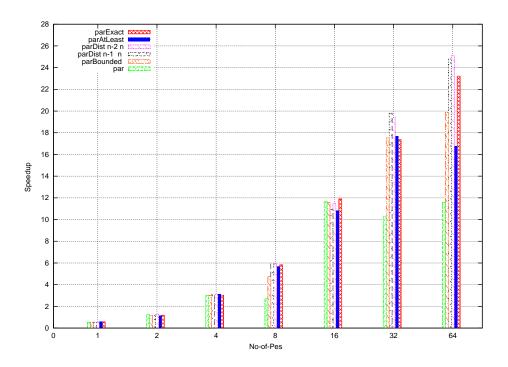

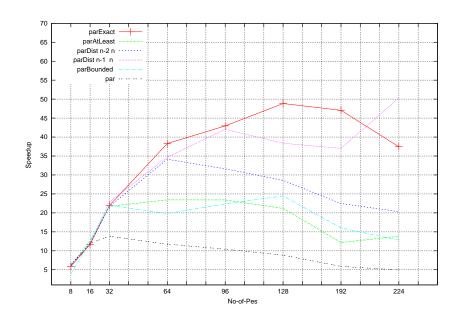

| 49 | parMapList Speedups (64 Cores)                    |

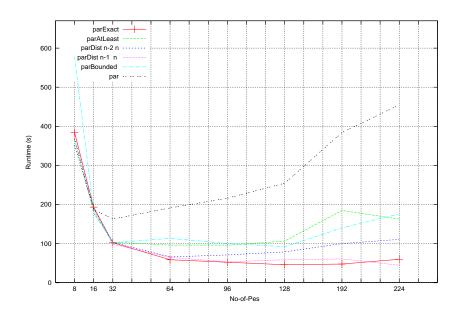

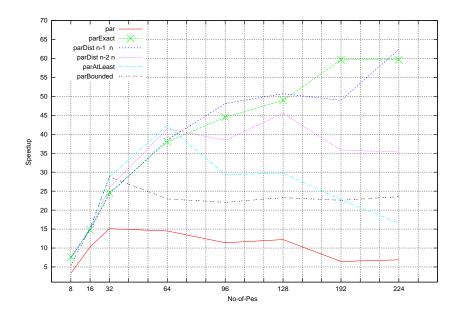

| 50 | parMapList Runtimes                               |

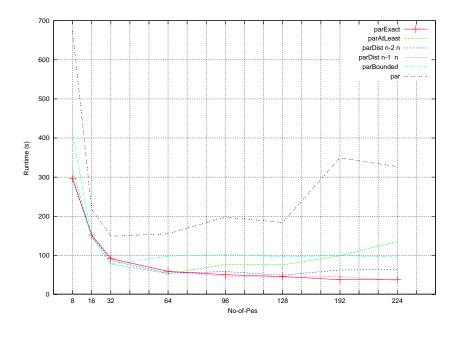

| 51 | parMapIntervals Runtimes                          |

| 52 | parMapList Speedups (224 Cores)                   |

| 53 | parMapIntervals Speedups (224 Cores)              |

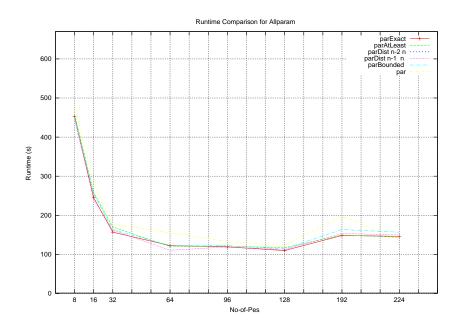

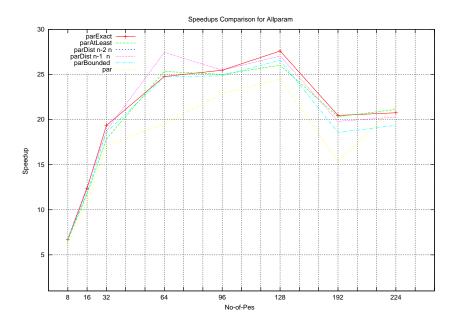

| 54 | Allparam Program                                  |

| 55 | Allparam Runtimes                                                      |

|----|------------------------------------------------------------------------|

| 56 | Allparam Speedups(224 Cores)                                           |

| 57 | findLevel Based on Input Argument                                      |

| 58 | findLevel Based on Depth of Recursive Call                             |

| 59 | Original parList                                                       |

| 60 | Architecture-aware parDistList Strategy                                |

| 61 | Architecture-aware parListLevel Strategy                               |

| 62 | Queen Top Level Function                                               |

| 63 | Architecture-aware sumEulerDist                                        |

| 64 | Sequential Map and Parallel parMap Skeletons                           |

| 65 | parMapLevel Skeleton                                                   |

| 66 | Monadic parMap Skeleton                                                |

| 67 | Monadic parMapLevel Skeleton                                           |

| 68 | General Parallel Divide-and-Conquer Skeleton                           |

| 69 | Architecture Aware Divide and Conquer Skeleton 191                     |

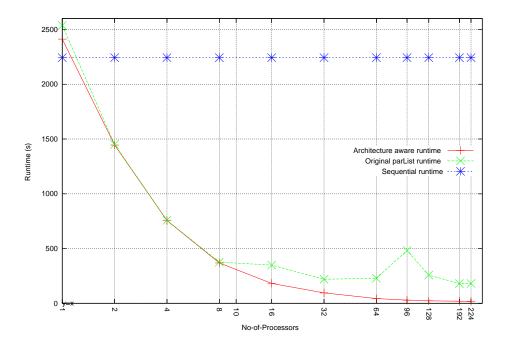

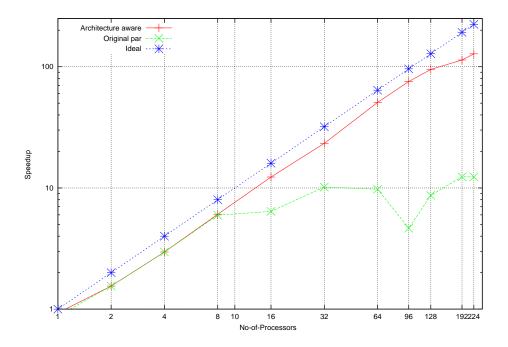

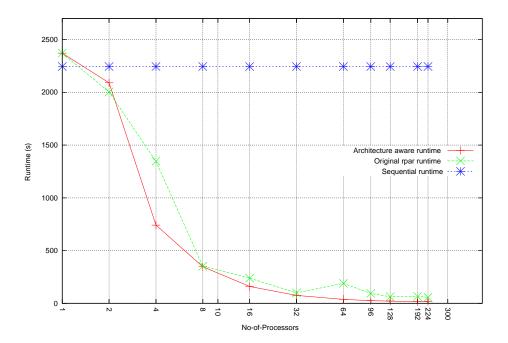

| 70 | Arch. Aware vs Orig. Strategies Runtime Comparison (sumEulerDist)193   |

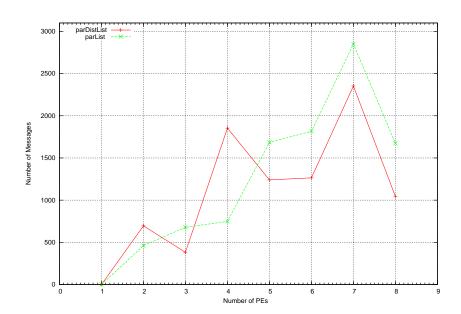

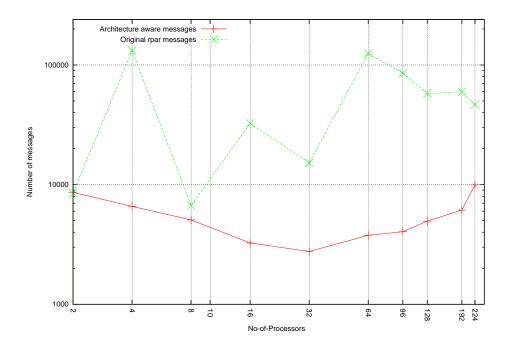

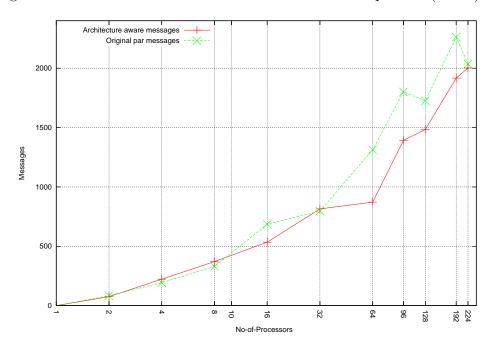

| 71 | Arch. Aware vs Orig. Strategies: messages Comparison (sumEulerDist)194 |

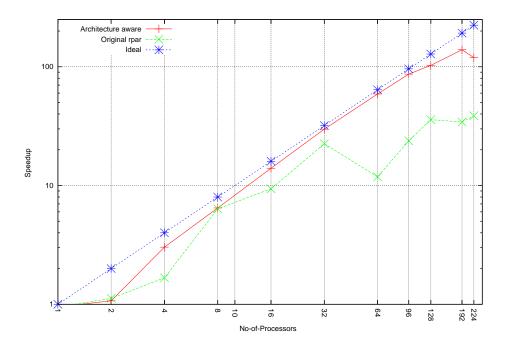

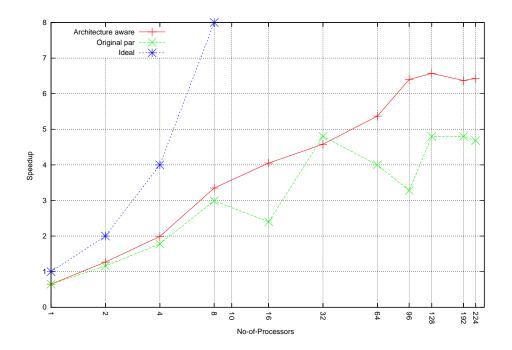

| 72 | Arch. Aware vs Orig. Strategies Speedup Comparison (sumEulerDist)196   |

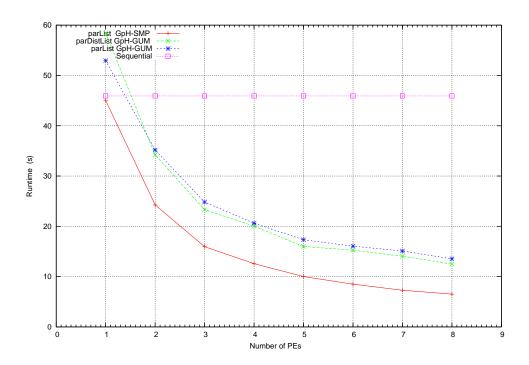

| 73 | Runtime Comparison on Shared Memory (Queen) 201                        |

| 74 | Speedup Comparison on Shared Memory (Queen) 201                        |

| 75 | Messages Comparison on Shared Memory (Queen) 203                       |

## $List\ of\ Figures$

| 76 | Messages Comparison on Distributed Memory (Queen) 203                |

|----|----------------------------------------------------------------------|

| 77 | Speedup Comparison on Distributed Memory (Queen) 205                 |

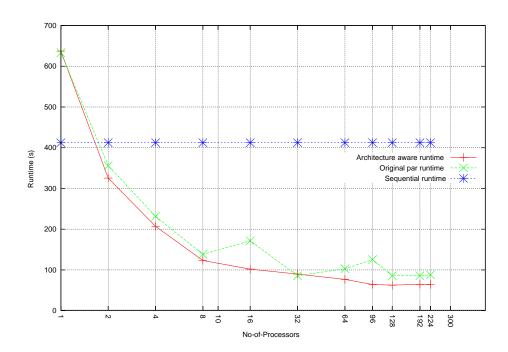

| 78 | Arch. Aware vs Orig. Skeleton Runtime Comparison (sumEulerSkel) 207  |

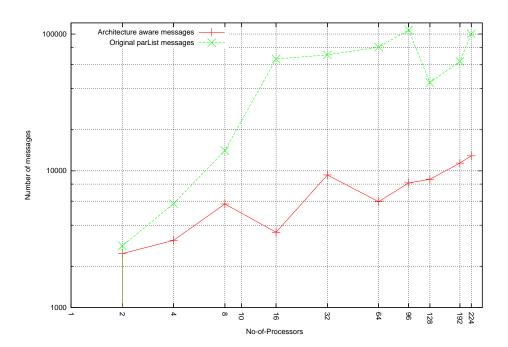

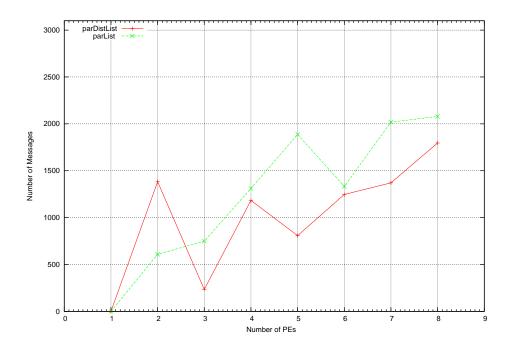

| 79 | Arch. Aware vs Orig. Skeleton Messages Comparison (sumEulerSkel) 208 |

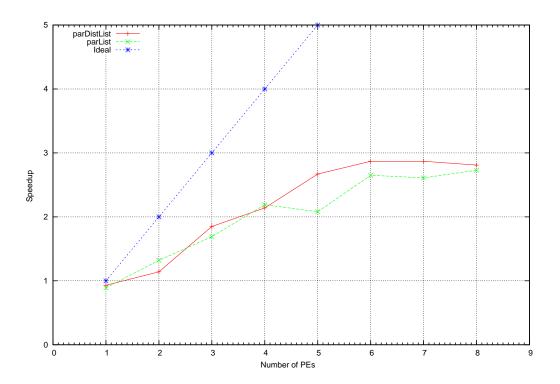

| 80 | Arch. Aware vs Orig. Skeleton Speedup Comparison (sumEulerSkel) 209  |

| 81 | Runtime Architecture Aware Skeleton Comparison (Coins) 212           |

| 82 | Messages Architecture Aware Skeleton Comparison (Coins) 212          |

| 83 | Speedup Architecture Aware Skeleton Comparison (Coins) 213           |

## Glossary

- **closure** represents a unit of computation and is evaluated by jumping to the code it points to. See also thunk.

- **FCFS** First Come First Served (FCFS) is a scheduling algorithm for dynamic real-time computer system in which tasks arrive as random process.

- **FDIP** Feedback Directed Implicit Parallelism (FDIP) is fully implicit parallel Haskell implementations..

- **GpH-GUM** Graph-reduction on a Unified Machine-model (GUM) is a portable, parallel runtime environment for GpH [121], designed for both shared and distributed memory architectures..

- **GpH-SMP** Glasgow Haskell Compiler (GHC) supports shared-memory implementation of Glasgow parallel Haskell (GpH).

- **NF** Normal Form (NF), if an expression is in its normal form status, it means that no further reduction can be made on the expression.

- parAtLeast is a parallel coordination construct that indicates that the expression may be executed in parallel and specifies the minimum distance in the communication hierarchy that the expression can be sent.

- parBound is a parallel coordination construct that indicates that the expression may be executed in parallel and specifies the maximum distance in the communication hierarchy that the expression can be sent.

- parDist is a parallel coordination primitive that indicates that the expression may be executed in parallel and specifies the execution boundaries in the communication hierarchythat the expression can be sent.

- parExact is a parallel coordination construct that indicates that the expression may be executed in parallel and specifies a specific execution level in the communication hierarchy that the expression can be sent.

- **PE** Processing Element (PE) is a core within a multicore machine. It may or may not associated with resources such as memory, disk, and screen.

- process A process is a program that is running on a computer. A computer is likely to have more processes running than actual program. In parallel programming a program is divided into multiple process with the objective of running a program in less time.

QuickCheck is a tool which aids the Haskell programmer in formulating and

testing properties of programs. Properties are described as Haskell functions, and can be automatically tested on random or custom test data input.

- rnf Reduce to Normal Form (rnf) means that reduce a given expression to a form contain no reducable expressions.

- rwhnf Reduce to Weak Head Normal Form (rwnf) means that reduce a given expression to its top constructor only.

- spark Spark is a pointer to an sub-graph indicates that the sub-graph can be evaluated in parallel.

- **sparkpool** is simply a set of pointers to computations that have been sparked by a parallel coordination primitive.

- **Thread** is a sequential computation whose purpose is to reduce a particular sub-graph to normal form. Threads are normally generated by a fork of a program in multiple parallel tasks.

- thunk represents an unevaluated expression which will be updated with its result. See also closure.

- **WHNF** Weak Head Normal Form is the evaluation of an expression to its top constructor.

## Chapter 1

## Introduction

For nearly half a century, processors have been in a constant development to meet the demand for computing capability. The development follows Moore's Law, where the number of transistors in an integrated circuit has doubled every two years [84]. Since 2002, however, the trend has reached a point where little further improvement can be achieved on a single processor, as clock frequency is constrained by power expenditure and heat generation. Hence, architectural design is driving to multicore architectures. However, a conventional single threaded program does not benefit from this new architecture. The performance may also suffer as a result of the lowered clock speed of each core. The shift towards new multicore architectures poses several challenges to software developers. These challenges aim to translate the potential processing power into an equal increase in computational performance.

Furthermore, future architectures will inevitably have a hierarchical, or tree-like, communications structure. The number of cores will steadily increase, as will the level of heterogeneity. Already the most common parallel architectures are clusters of multicore nodes, with three communication level in the hierarchy: on-core, sharing memory, on another node. The communication hierarchy is likely to become deeper as the number of cores increases. Heterogeneous parallel architectures have several different types of processing units, each of which is intended to execute a specific set of tasks. For example, graphics processing units (GPUs) are now present in commodity computer systems [102]. GPUs are specifically designed to take advantage of data parallelism and have significantly better floating point performance than an equivalent CPU. Field Programmable Gate Arrays (FPGAs) are another type of processing unit. FPGAs are non-conventional processors built primarily out of logic blocks connected by programmable wires [35].

This research is intended to exploiting only the heterogeneity of cores in clusters of multicores. To exploit such architectures, programming models must be aware of the communication hierarchy. Given the rate of architecture evolution it is important that the programming model preserves performance portability as far as possible.

The target of this work is to develop a high-level programming model for hierarchical architectures. The philosophy is to move the responsibility of task placement, load balance, thread creation, and synchronisation from the application developer to the runtime system. However, the proposed approach keeps some control of parallel aspects, e.g. data locality and task allocation. The intention is that applications can exploit the potential performance of hierarchical architecture with minimal parallel coordination.

## 1.1 Thesis Statement

Given the difficulties involved in programming hierarchical architectures, this thesis asserts that an architecture-aware programming model with a high level of abstraction can effectively exploit hierarchical architectures. The assertion is demonstrated by providing an architecture-aware programming model that exploits the underlying architecture. GpH-GUM is extended to record the communication topology of the architecture for task placement. The performance of the architecture-aware programming model is evaluated by measuring a set of demonstration benchmarks on a hierarchical architecture.

The GpH-GUM implementation was ported from the early GHC-4.06 version to the considerably enhanced GHC-6.12 version. The work involved modifying many of the runtime system functions, as GHC-6.12 introduces many new features: new closures types, new data types, and new functions. Some modifications are also required to the compiler. This process took eight months to finish. While the current port successfully executes small programs, there are still

unknown stability issues, in particular the system fails for programs with large data structures.

## 1.2 Contributions

This thesis investigates parallel functional programming on multicore and distributed memory architectures. A primary contribution is to develop and evaluate new high level architecture-aware programming constructs for hierarchical parallel platforms.

- We propose four new architecture-aware constructs for GPH that exploit information about task size and aim to reduce communication for small tasks, preserve data locality, or to distribute large units of work. We define a semantics for the constructs that specifies the sets of PEs that each construct identifies and we check several properties of the semantics using Quickcheck. We investigate three common paradigms, data parallelism, divide-and-conquer and nested parallelism, on hierarchical architectures with up to 224 cores. The results show that the new constructs consistently deliver better speedup and scalability than existing primitives, together with a dramatic reduction in the execution time variability. At times, speedup is improved by an order of magnitude [9] (Section 5.6).

- We make a preliminary investigation into architecture-aware programming models that abstract over the new constructs. In particular, we propose

architecture-aware evaluation strategies, and architecture-aware skeletons. The abstractions aid performance portability by isolating architecture-specific aspects of the program. The new abstractions are used in the programs measured and the performance results are promising [9] (Section 5.6, Chapter 6).

- We demonstrate the first programming and performance comparison of four functional multicore technologies and report some of the first ever multicore results for two parallel Haskell languages, GpH and Eden. The comparison contrasts the programming effort each language requires with the parallel performance delivered. The study uses 15 typical programs to compare a "no pain", i.e. entirely implicit, parallel language with three "low pain", i.e. semi-explicit languages. There are many encouraging signs for multicore functional languages. The GpH and Eden semi-explicit approaches deliver effective high level coordination, and hence require very small program changes, and modest effort to introduce and tune the parallelism, for a known program [8] (Chapter 3).

- We investigate the most profitable thread granularity required to achieve satisfactory performance for a distributed memory parallel functional language on a multicore platform. We address the question by undertaking a limit study and by studying more typical programs. The programs cover

<sup>&</sup>lt;sup>1</sup>In contrast, much parallel programming is high pain for high gain. For example GPUs or classic HPC programming requires the programmer to expend intense programming effort to obtain the best possible parallel performance.

both divide-and-conquer and data parallel paradigms. The limit study identifies the most profitable thread granularity required to gain good performance from a message-passing semi-explicit functional language like Eden on a multicore architecture [3] (Chapter 4, Section 4.2).

• We have implemented and investigated the performance of a new formulation of evaluation strategies on a selection of parallel Haskell benchmarks [77] (Chapter 4).

## 1.3 Thesis Structure

Chapter 2 reviews relevant issues in the area of general purpose parallel computing architectures. It outlines the new trends towards hierarchical communications architectures. Parallel programming approaches are reviewed and discussed. At the end of the chapter, we outline the runtime aspects that are crucial to the implementation of implicit or semi-explicit parallel functional languages.

Chapter 3 presents the findings of the comparison of four different parallel Haskell implementations on multicore architecture. It outlines the key features, programming effort, and performance of each implementation.

Chapter 4 outlines the first uses of a new formulation of evaluation strategies for GPH by undertaking a systematic benchmarking of the new formulation. The chapter also investigates the thread granularity required to achieve acceptable

performance from a distributed-memory parallel functional language, i.e. Eden and GPH, on multicores.

Chapter 5 presents the design of new architecture-aware constructs for the GPH language which can exploit information about task size and aim to reduce communication for small tasks, preserve data locality, or distribute large units of work. The architecture-aware constructs provide multiple levels of parallelism to maximise the performance of new architectures. The behaviour of the architecture-aware constructs is also investigated.

Chapter 6 presents preliminary investigations of architecture-aware programming models that abstract over the new constructs. Specifically, we present some key abstractions and demonstrate some architecture-aware evaluation strategies and skeletons.

Chapter 7 concludes and suggests the opportunities for future work that may extend the work presented in this dissertation.

## 1.4 Authorship and Publications

Unless otherwise stated the work presented throughout this doctoral thesis was authored by myself and the work contained herein is my own. As a result of the research activities the following research papers were published:

[8] Aswad, M., Trinder, P., Al Zain, A., Michaelson, G., and Berthold, J. Low

- Pain vs No Pain Multi-core Haskells. TFP09, Sympo- sium on Trends in Functional Programming, Komarno, Slovakia 10 (June 2009), pp. 4963.

- [3] Al Zain, A., Hammond, K., Berthold, J., Trinder, P., Michaelson, G., and Aswad, M. Low-pain, High-gain Multicore Programming in Haskell: Coordinating Irregular Symbolic Computations on Multicore Architectures. In Proceedings of the 4th workshop on Declarative aspects of multicore programming (2009), ACM, pp. 2536.

- [77] Marlow, S., Maier, P., Loidl, H.-W., Aswad, M. K., and Trinder, P. Seq no more: Better Strategies for Parallel Haskell. In Proceedings of the 3rd ACM SIGPLAN symposium on Haskell (Baltimore, MD, United States, Sept. 2010), ACM Press, pp. 91102.

- [9] Aswad, M., Trinder, P. W., and Loidl, H. Architecture-Aware Parallel Programming in Glasgow Parallel Haskell (GPH). In Proceedings of the International Conference on Computational Science (ICCS) (Omaha, USA, June 2012), Procedia Computer Science, pp. 18071816.

The content of the papers is related to the chapters of the thesis as follows:

• In [8], we present a programming and performance comparison of functional multicore technologies material for four parallel Haskell implementations (Chapter 3).

#### Chapter 1. Introduction

- In [77], we present a performance evaluation of the new Eval monad strategies material (Section 4.1.3).

- In Section 6 of [3], we present the results of the thread granularity limited study on multicores (Section 4.2).

- In [9], we describe the design of the new architecture-aware constructs for the parallel Haskell extension GPH material (Chapter 5).

## Chapter 2

## Background

### 2.1 Parallel Hardware

Up until recently, improvements in performance of commodity machines relied on increased clock frequency and instruction-level parallelism. However, the amount of instruction-level parallelism that can be extracted from sequential programs is limited [110], and since 2002, CPU clock frequency increases have stalled, due to power and heat issues [101]. Therefore, the whole microprocessor industry has turned to manufacturing processors incorporating multiple cores onto a single die [12]. These architectures are known as multicores. These multicore machines are becoming the predominant architecture for general propose computing systems. In such environments, heterogeneity occurs in several forms: e.g. PEs may have different instruction sets, different operating systems, or there may be different network connections between PEs [111].

## 2.1.1 Classification by Memory Structure

Parallel architecture can be classified as shared memory or distributed memory. In a shared memory system, cores share a single address memory space. Typically, this is implemented through a shared bus, although this design is limited to a few dozen cores. In a distributed memory system, each core has exclusive access to its own local memory, whereas this memory space can be logically or physically distributed [106]. Separately from the physical structure of memory, it can be logically distributed or virtually shared. These forms of logical organisation can be combined with underlying physical structure by e.g. implementing a virtual shared memory abstraction. In addition to the memory structure, each core (Processor Element) has a private cache and possibly shares the cache with other local cores (e.g. L2 cache). The L1 cache is located close to the core and is used to store blocks of values required by the process executing on the core to exploit data locality. Cores may share the standard Random Access Memory (RAM) through a common bus.

Thus, modern architectures realise a deep memory hierarchy of remote memory, local memory, (several levels of) cache and register, with decreasing access time and decreasing size. Efficiently exploiting this memory hierarchy is crucial for high-performance computing.

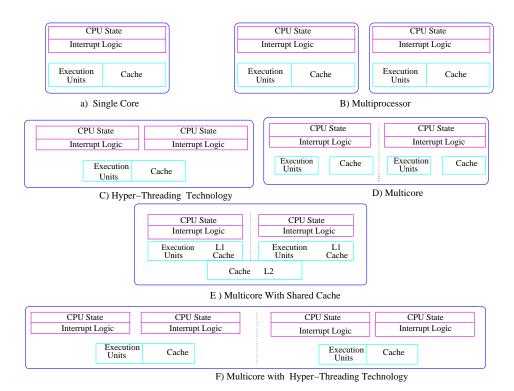

Figure 1: Comparison of Single Core and Different Multicore Architectures([2])

#### 2.1.2 Multi-core Architecture

Multicore devices have been around for many years, in different forms [113]. Most of them are homogeneous devices consisting of several identical cores to form a multicore. However, future multicore systems will be heterogeneous multicore devices, including several cores with different capability [42, 60]. The homogeneous option is used in most of today's systems because it is easy to implement. An example a simple multicore system is a dual core system containing two identical cores within a single die, which aims to double the performance [62, 20]. Figure 1 illustrates typical multicore architecture, specifically some Intel multicore architectures and their memory topologies:

- a) A single core consists of core and cache.

- b) A multiprocessor consists of two identical chips where each has its core and cache.

- c) Hyper-Threading on a single chip consists of a core with two or more CPUs and interrupt logic.

- d) A multicore chip consists of two cores where each has its own cache.

- e) A multicore consists of two cores sharing only L2 cache.

- f) A multicore consists of two hyper-threaded cores sharing a cache.

In a dual core, the performance can be increased without any software modification as the operating system can dedicate one core for the main application and the other core for a specific task such as interrupt handling. However, in a multiple core device, it is desirable to use several cores to execute one user application and the application must be reshaped to make use of all the cores for optimal performance.

## 2.1.3 Homogeneous vs Heterogeneous Multicore

Today systems for massive parallelism often consist of several homogeneous clusters of different speeds and sizes interconnected through traditional networks, which means the architecture becomes heterogeneous [112]. A heterogeneous architecture has the advantage that it may improve performance and efficiency, both

through increased specialisation of core types and the large numbers of processors. The objective is to provide better balance between sequential and parallel workload. The different core capability of heterogeneous architectures are usually developed in a way that each core is dedicated to a different workload. The most powerful core is assigned to perform heavy tasks, e.g. operating system actions. In contrast, cores in homogeneous architectures are treated equally but not specialising any of the cores for a particular task. It is therefore very difficult to distribute an irregular parallel workload in a manner that balances the workload between cores [82]. The property of easy construction and mapping tasks in homogeneous parallel architectures, which are usually in a single machine or single cluster, will soon be unavailable because of the increasing number of cores in a single chip. This increase will allow the construction of multicore machines with cores of different capabilities.

## 2.1.4 Distributed Computing

A distributed memory system is a system in which the processing elements are connected by a network. Several computing paradigms can be considered as distributed computing: cluster computing, Grid computing and, more recently, Cloud computing. Sadashiv [104] has presented a detailed comparison between the three architectures. Buyya [23] defines these paradigms as "a cluster is a category of parallel and distributed platform, which consists of a collection of

interconnected standard computers working jointly as a single incorporated computing resource". A Grid is a parallel and distributed architecture that enables sharing of resources dynamically at runtime system level [1]. A Cloud is a parallel and distributed architecture consisting of a collection of interconnected and virtual parallel computers. It can be provided dynamically and viewed as a single or several computing resources depending on consumers needs.

This thesis primarily focuses on clusters, e.g. the proposed model is evaluated on a group of interconnecting clusters in Chapter 6.

Cluster Computing consists of multiple standalone computers connected by a local area network. Computers in one cluster should be identical to minimise the difficulty of achievement of the load balance. The most common type of such a cluster is the Beowulf cluster [99], which consist of multiple interconnected (identical) commercial off-the-shelf computers. Commonly, the ordinary network technology is used [109]. With multicores becoming standard machines, the individual nodes in the clusters are themselves dominant. This architectural change has complicated the implementation of load balancing and has introduced additional challenges to parallel programming developers. They have to take advantage of multicore features in their software development. One of the most important features that needs to be captured is the hierarchical memory structure, which can be achieved by exploiting data locality in a parallel program [5].

Grid Computing is a collection of computer resources where computing is executed over a network. This approach is viewed as one set of a virtual global community, where resources are heterogeneous. This virtual community is geographically distributed and belongs to different organisations. Grid are used to solve comprehensive computational problems in science, engineering, and commerce [11].

Hybrid Architecture is a high speed parallel computing architecture consisting of several nodes with private address space. A hybrid architecture can be viewed as a combination of Von Neumann features and Dataflow features [50]. It is an array of identical processors, connected through a suitable switching network to a global memory. Moreover, a hybrid architecture can take different forms: it can be a small cluster of single core machines or cluster of multicore machines. It can also be geographically distributed clusters connected by a network.

Hierarchical Architectures: These are geographically distributed hierarchical architectures [22]. Moreover, even common parallel clusters of multicore nodes can be considered as hierarchical, with three hierarchy levels. Threads on the same core can communicate most efficiently with a thread on the same core, more slowly with a thread on another core in the node, and even more slowly with threads on remote nodes. The communication hierarchy is likely to become deeper as the number of cores increases. For example, the number of cores sharing the same memory is likely to be restricted, and hence many core architectures

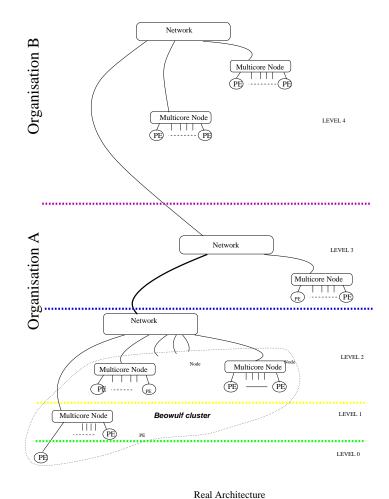

Figure 2: Hierarchical Architectures

may introduce another level within a node.

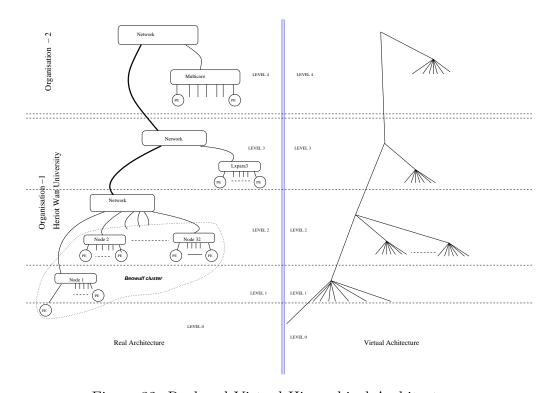

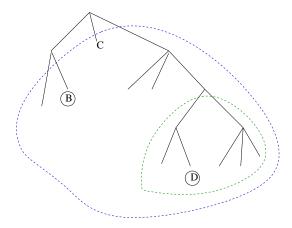

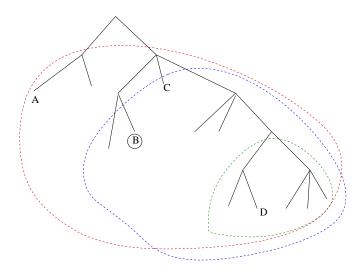

Figure 2 illustrates a hierarchical architecture of two organisations A & B.

The architecture can be viewed as an unbalanced tree of nodes.

### 2.1.5 Summary

The increasing deployment of multicore architectures brings parallel computing into the mainstream. This paradigm shift creates a challenge of parallel programming and system understanding in general. Clusters are the dominant server technology and can be constructed from various computer types.

| Mamaann       | Single | Multi-Core           | Symmetric            | Distributed     |

|---------------|--------|----------------------|----------------------|-----------------|

| Memory        | Core   | L1+L2                | Multi-Core (SMP)     | Memory          |

| Own Cache     | Yes    | Yes                  |                      | Yes             |

| Own Ram       | Yes    |                      |                      | Yes             |

| Shared Cache  |        | Yes                  | Yes                  |                 |

| Shared Ram    |        | Yes                  | Yes                  |                 |

| Communication |        | coordinated accesses | coordinated accesses | Message Passing |

Table 1: Memory Classification

Table 1 summarises the types of computers from a memory perspective. The first column shows the comparison categories. The second column shows a single core architecture where nothing is shared. The third column presents a multicore architecture in which memory appears in the form of a hierarchy: each core has it own cache and two cores have a shared cache, and in addition to that all cores share the same RAM. The fourth column shows a symmetric multicore architecture; cores share both cache and RAM. The final column shows a distributed memory architecture, where each core has a local cache and RAM, and a bus or network interconnects all cores. Cores within multicore and SMP communicate with each other through memory access. In contrast, cores in distributed memory communicate through message passing.

Heterogeneous multicores and clusters consisting of these different kinds of processors are becoming the predominant architectures. This trend needs a matching programming model to exploit the potential performance.

## 2.2 Parallel Programming Classifications

Since hardware is parallel by default nowadays, software must become parallel, too. This requires modifications to the existing software to cope with new parallel architectures. For many application a key requirement of the parallel programming model is that it has to be easy. In particular, it should not be much more difficult than the traditional sequential programming model. Of course, there are other requirements like maintaining the existing sequential software, portability and, most of all, the performance. The main challenge in parallel language design is to find a suitable balance between performance and abstraction. To start with, the application must be designed in a manner that can be parallelised i.e. decomposed into a number of tasks that can be executed in parallel. This section discusses a number of alternative parallel programming languages.

Before the parallel software development process is studied in general, we have to explain the two possible types of parallelism in any given application: data parallelism or task parallelism.

Data parallelism describes a type of parallelism where a function is applied to multiple data items simultaneously. It can be flat data parallelism, where the function is applied to a one dimensional data set, or nested data parallelism, where the function is applied to a many dimensional data set. It is not necessarily the case that the same function is applied to both dimensions. It may happen that different functions are applied to different dimensions. Parallel array computation

is the most common approach used by many data parallel languages such as NESL [21], High Performance Fortran (HPF) [29], ZPL [26], and Hierarchically Tiled Arrays (HTAs) [17].

Task parallelism is a form of parallelism where computational units, e.g. functions, are distributed to be executed in parallel. The key notion is that an application has to be divided into several independent tasks. These tasks can be mapped automatically onto physical processors [6]. The scheduling of the tasks to the physical processors is usually performed by the implementation.

There are a number of important parallel paradigms and this section focuses on those related to the thesis. Some important paradigms not covered here include Single Program Multiple Data (SPMD) [51], Bulk Synchronous Processes (BSP) [123], and the increasingly important GPU programming models like CUDA [102] and OpenCL [85].

### 2.2.1 Parallel Software Development

Parallel software development has a number of distinctive issues in addition to issues inherited from sequential software development. Either the programmer or the compiler is responsible for addressing these issues [41, 96]. The following are the distinctive issues related to parallel software development:

- Exploitation of the Potential Parallelism: the algorithm should indicate the source of parallelism existing in the problem. This involves partitioning the program into sequential parts that can be performed in parallel. However, exploiting every single source of parallelism is not always the best choice because this generates extremely small pieces of computation, for which the system overhead dominates the computation.

- Resource Utilisation: the exploited parallelism has to be mapped to parallel hardware in a way to make efficient use of the available resources. For example a program should utilise a suitable number of cores, and make limited memory and communication demands. The efficiency of the parallelism depends on the programmer and on the parallel software model involved. High efficiency can be achieved by statically grouping tasks and scheduling their execution on cores equally or by achieving the load balance at runtime by assigning tasks to idle cores.

- Synchronisation & Communication: communication in parallel programming refers to the information exchange between parallel computations. The information exchange between parallel computations requires some form of synchronisation, either implicit or explicit. Synchronisation can be achieved by either shared variable communication primitives that control access to critical sections or message passing communication primitives, which guarantee exclusive access to shared objects. It is crucial to

avoid deadlock, starvation and non-termination.

- Correctness of parallel implementation needs to be preserved. Because parallelisation often requires structural changes to the code, as well as additional coordination code, assuring that the parallel program produces the same result as the sequential program is non-trivial. Not only must the result be correct but the performance must be reasonable. In parallel programs, we may get the correct result, but at the price of losing performance as a result of unequal distribution of tasks among processors.

- Parallel Software Debugging is the process of testing the parallel program and improving the performance. Tracking errors in parallel software (especially performance errors) is exceptionally difficult. There are tools to aid this process that give an overview of the cores' status at any given moment of the program execution. This is manageable for a small number of cores, but for a large number of cores, say thousands, this will be extremely difficult.

## 2.2.2 Parallel Programming Models and Languages

Parallel programming models can be classified in several ways to determine their suitability for challenges such as portability, efficiency and ease of programming. Unfortunately, these properties conflict with each other. For example, for ease of programing, the programmer can ignore the underlying architecture in their

application. However, high performance may require that the programmer gives some details about the underlying architecture. The more specified the architecture, the less the application will be portable and thus the higher the maintenance cost.

Parallel programming languages can be classified into imperative approaches and declarative approaches. An imperative parallel programming language [118] represents a computation as a group of interacting parallel tasks that communicate and synchronise using message passing, shared memory locks or via remote procedure call. The strength of the imperative is in explicitly representing tasks and operations from the problem specification and thus achieving detailed control of the parallel programming. Its disadvantage is the difficulty of expressing parallelism and the interaction patterns of its operations. In contrast, declarative parallel programming [73] represents the logic of computation without describing its control flow. Due to referential transparency, expressions can be evaluated in any order, in particular also in parallel. Thus, correctness of the parallel programming is often trivial. The coordination of the parallelism is typically managed by the compiler and by the runtime system. Consequently, programmers only have to deal with the decomposition of their problems into parallel tasks.

Skillicorn and Talia [106] categorised parallel models based on their degree of abstraction.

• Nothing Explicit (Implicit) models hide all parallel details from the

programmer. The programmer continues to program in a sequential manner. These are easy to use and highly abstract, but potentially inefficient.

- Explicit Parallelism (semi-Explicit) models require a programmer to expose the inherent parallelism in the program. However, the runtime system is responsible for determination of the actual parallelism, execution, mapping, communication and synchronisation.

- Explicit Decomposition models require a programmer to indicate the potential parallelism inherited from the program and divide this parallelism into tasks but to allow the placement of the tasks be decided by the runtime system.

- Explicit Mapping models require a programmer to indicate the potential parallelism inherited from the program: how the program is divided into pieces and where to place each task. However, the communication and synchronisation are left to the runtime system.

- Everything Explicit models require a programmer to identify all parallel details activities. It is extremely difficult to write an application using such models, because both correctness and performance can only be reached by knowing large number of complex details of the system and underlying architecture.

Loogen[71] classifies parallel programming models with respect to the level of

|                          | Control Parallelism                                                            | Data Parallel               |

|--------------------------|--------------------------------------------------------------------------------|-----------------------------|

| Implicit                 | automatic parallelisation                                                      | data parallel languages     |

| Controlled semi-Explicit | annotation based languages<br>evaluation strategies<br>skeleton languages      | high-level data parallelism |

| Controlled Explicit      | process control languages<br>message passing languages<br>concurrent languages |                             |

Table 2: Classification of Parallel Models

control and type of parallelism. The models are split into three categories. With implicit approaches, the system tries automatically to exploit the parallelism that is inherent in the semantics. With controlled approaches, the programmer is involved in inserting a notation either to exploit parallelism or to control the execution behaviour. With explicit approaches, a programmer is required to describe all parallel aspects in the program. Table 2 shows Loogen's classification.

## 2.2.3 Implicit Models

In an implicit model, the compiler automatically exploits the parallelism available in the computations [71]. There is no need for special directives, operators or functions to enable parallelism. Therefore, the job of the implementer of the language becomes much harder, since the compiler and/or runtime system must infer all parallel structures of the eventual program [59]. Ideally, automatic parallelisation would exploit all the potential parallelism of reasonable granularity. Whether generating parallelism is worthwhile heavily depends on the size of the

expression and the underlying architecture characteristics. Therefore, information about thread granularity is often involved in deciding the size of expression that should be evaluated in parallel. There are many implicit parallel models available. The rest of this section discusses some prominent systems supporting implicit parallelism.

Intel has developed an automatic partitioning packet processing applications compiler for pipelined architectures [33]. This approach automatically splits a sequential C code into coordinated pipeline parallel subtasks. These tasks are mapped to processing elements of a network or parallel architecture. The technique allows a minimisation of data transfer between subtasks and a balance of processing tasks in the pipeline. Using this compiler, the programmer can continue to write applications in a sequential manner even if they should be executed on heterogeneous multicore architecture. Nevertheless, the extraction of parallelisation depends on the amount of inherent data parallelism from the algorithm and its dependencies.

Feedback Directed Implicit Parallelism (FDIP) is an implicitly parallel implementation of the Haskell functional language [46]. FDIP extracts potential parallelism from sequential Haskell code in four processing stages. In the first stage, it executes and profiles the sequential code. In the second stage, it analyses the profile output to identify useful sources of parallelism. A Haskell program

usually contains a large number of potential computation thunks, which may represent useful sources of parallelism. However, the hard question is: which of these are suitable for potential parallelism. In the third stage, the program is automatically recompiled to introduce parallelism at the identified sites. In the final stage, the output of stage three is executed on sophisticated mechanisms implemented in the GHC runtime system. The implementation dynamically manages thread generation and load balance.

### 2.2.4 Semi-Explicit Parallel Models

A semi-explicit parallel model requires the programmer to indicate the source of potential parallelism in the algorithm, whereas the decision of realising the actual parallelism is left to the compiler or to the runtime system. Annotations to the compiler are used to identify sources of parallelism in the algorithm, and hence to control the parallel behaviour of the algorithm, whilst hiding the low level implementation details from the programmer. The annotations affect only the run-time behaviour of programs, but not the result.

**OpenMP** uses an imperative parallel programming style [28]. It is a portable programming interface for shared memory multithreaded programming using C/C++ and Fortran as host languages. OpenMP consists of a set of compiler directives, library routines, and environment variables that affect run-time behaviour. OpenMP uses a fork-join threading model; a master thread forks a

task into a number of worker threads that share the work and then wait until they finish to join before continuing. OpenMP is a scalable model that gives programmers a simple and flexible interface for developing parallel applications for a range of parallel architectures. The model is identified as easy to use and portable. The programmer does not need to put significant effort into parallelising the existing sequential program. However, this is not always the case, as the multicore resources are not fully utilised if the programmer is not expert in parallel programming.

High Performance Fortran (HPF) is a standardised imperative parallel language, which focuses mainly on the issues of distributing data across the memories of a distributed memory multicore [29]. It is an extension of Fortran90 that exploits data parallelism. Data parallelism exists when a single operation is carried out over a collection of data. HPF adds a set of directives such as Processors, Distribute and alignments directives. Processors allocates the number of abstract cores. It is usually equal to the number of actual physical cores. Distribute distributes the data in an array along cores in a combination of operational groups, and or block modes.

The Manticore project combines NESL style data parallelism with more general task parallelism as found in some other languages such as Concurrent ML (CML) [98]. In a sense, it represents a heterogeneous parallel language [40, 25]. Manticore combines features of CML supporting explicit concurrency as well as

of NESL data parallelism. It is based on three components: sequential functional programming features of SML; explicit concurrent programming primitives using threads and synchronous message passing inherited from CML; and implicit nested data parallelism from NESL and Nepal[24]. The underlying hardware topology can be hidden behind data and type abstraction using a CML abstraction mechanism called first-class synchronous operations. Using event values, programmers can easily specify very complicated communication and synchronisation protocols. Parallel arrays in Manticore can be of any type and they can be nested. The compiler maps parallel array operations onto appropriate parallel architecture.

NESL is a strict, strongly-typed, nested data-parallel language with implicit parallelism and implicit thread interaction [21]. It has been implemented on a variety of parallel architectures, including several vector computers. NESL fully supports nested sequences and nested parallelism. The language allows a programmer to perform a higher-order function on a list in parallel. NESL is loosely based on the ML functional language. In NESL the Apply-to-each is the central construct to exploit parallelism. This construct uses a set-like notation. NESL uses a method based on asynchronous core groups to reduce communication and a run-time load-balancing system to cope with dynamic data distributions. This is achieved by translating the user's algorithm into ANSI C with MPI calls, and linking this code with an MPI (Message Passing Interface) library.

Glasgow Parallel Haskell (GpH) is a modest extension of Haskell98 [121]. It uses a thread-based approach to parallelism. This approach allows the creation of parallel threads, but does not require mechanisms to control them. Synchronisation is implicit through shared variables. It exploits different types of parallelism such as data parallelism and divide-and-conquer parallelism by defining a higher order function which combines coordination primitives. Evaluation strategies [121] are the preferred mechanism of high-level coordination of parallelism. GPH extends Haskell98 with parallel par and sequential pseq composition primitives (see Figure 3). Denotationally, both primitives are projections onto the second argument. Operationally, pseq causes the first argument to be evaluated before the second and par indicates that the first argument can be evaluated in parallel with the second argument. The latter operation is called sparking of parallelism and it is implemented using a lazy task creation approach. A spark in GPH is not immediately converted to a thread. The runtime environment is responsible for determining which sparks are going to be converted to parallel threads based on load and other information.

```

par :: a -> b -> b -- parallel composition

pseq :: a -> b -> b -- sequential composition

```

Figure 3: Types of the basic coordination constructs in GpH

Several implementations of GPH are available for parallel architectures. The GpH-SMP is an optimised shared memory implementation integrated into GHC from version 6.6 onwards [16]. The GpH-GUM implementation is a message-passing implementing a virtual shared heap [121]. The GpH-GUM has been ported from GHC version (GHC-4.06) to the recent GHC version (GHC-6.12) as part of this thesis.

Caliban is a declarative parallel programming language defined on top of the Haskell functional programming language [57, 114]. Caliban defines aspects of parallel runtime behaviours of the application program using annotations. The annotations do not effect the result produced by the program, although they can affect the termination properties of the program. As with GPH, the coordination level does not affect the result, although it can affect the termination properties of the program. The coordination-level entities in Caliban are processes that are connected by streams. Processes in the Caliban form a cyclic graph whose nodes are the physical processors and arcs are streams of data. The potential parallelism is gained from the data dependencies of the application. The Node construct is used to place the expression in a separate processor, where the Arc construct is used to connect nodes reflecting the data dependencies in the programme. The use of higher-order functions in the Caliban coordination language facilitates code re-use.

Clean is a pure concurrent lazy functional language [95]. It provides higherorder functions supporting concurrent processes and distributed execution, making use of an I/O library included in the language. Clean can dynamically create processes, which may run interleaved or in parallel. The interconnection between processes such as communication and synchronisation is handled automatically by the runtime system. However, the process topology can be defined by programmer using higher-order functions. Clean has been extended with a set of primitives in D-CLean [48]. These new primitives allow programmers to distribute computation in several layers. These layers can be distributed easily over clusters. The details of the underlying architecture can be hidden from the programmer using skeletons. The primitives that D-CLean provide are: DStart starts the distributed computation. DStop receives and saves the result of the computation. DApply applies the same function expression in parallel n times.

Eden [15] extends Haskell with syntactic constructs to explicitly define and instantiate processes. In contrast to the other languages, such direct Eden programming exposes parallel tasks at the language level, and requires the programmer to manage them using the control mechanisms provided in the language. In practice however, Eden provides libraries of skeletons [13] for parallelising applications.

Eden supports a distributed memory parallel paradigm. That is, processes share no values, and communicate only by messages. It might be thought that such a paradigm would not be suitable for parallelism on shared-memory multicore architectures; however recent results have shown good performance [16].

In direct usage, Eden is explicit about process creation and about the communication topology, but implicit about other control issues, such as sending and receiving messages and process placement. Granularity is under the programmer's control because he/she decides which expressions must be evaluated as parallel processes, and also some control of the load balancing is possible, at the program level.

Eden provides process abstractions and process instantiations for coordination, as shown in Figure 4.

Figure 4: Basic Coordination Constructs in Eden

The expression process ( $\x -> e$ ) of a predefined polymorphic type Process a b defines a process abstraction that takes a function of type (a->b) and constructs an analogous Process a b. When instantiated, processes are executed in parallel and if the output or input expression is a tuple, a separate concurrent thread is created for the evaluation of each tuple element. We refer to each output tuple element as a channel. A process instantiation is achieved with the predefined infix operator (#), and the Trans context supports the transmission of lists as streams and the creation of threads for tuple elements. Each time an

expression e1 # e2 is evaluated, a new process is created to evaluate the application of e1 to e2. We will refer to the latter as the *child* process, and to the owner of the instantiation expression as the *parent* process. The instantiation semantics specifies in which processes these expressions shall be evaluated: (1) Expression e1 together with its whole environment is *copied* in the current evaluation state to a new processor, and the child process is created there to evaluate the application of e1 to e2, where e2 must be remotely received. (2) Expression e2 is eagerly evaluated in the parent process. The resulting full normal form data is communicated to the child process as its input argument.

Once processes are created, only fully evaluated data objects are communicated. The only exceptions are lists: they are transmitted in a *stream*-like fashion, i.e. element by element. Each list element is first evaluated to full normal form and then transmitted. Processes trying to access input not yet available are temporarily suspended. This is the only synchronising mechanism in Eden.

Algorithmic skeletons in Eden abstract common patterns of parallel evaluation into higher order functions [32]. They simplify the development of parallel programs by hiding coordination details from the programmer and may provide ready-made parallel cost models.

Para-Functional parallel programming is based on a functional programming model enhanced with features that allow programs to be mapped to specific multiprocessor topologies [49]. There are extended control clauses, which can be

used to express quite sophisticated placement and evaluation schemes. These control clauses effectively form a separation between the language and process control. Parallelism may be exploited by a number of annotations such as \$on, send, receive. The compiler generates parallel PACLIB C with explicit task creation and synchronisation statements.

X10 is a parallel programming model under development at IBM for programming hierarchical parallelism [30]. X10 increases performance by integrating new constructs (notably, places, regions and distributions) to model hierarchical parallelism and nonuniform data access. X10 provides four storage classes: