### CHERIOT

#### **Robert Norton-Wright**

Saar Amar, Tony Chen, David Chisnall, Wes Filardo, Kunyan Liu, Hongyan Xia Microsoft

### IoT

The 'S' stands for security

### Motivation – IoT and embedded

The IoT ecosystem:

Includes diverse codebases Mostly unsafe C/C++ Mitigations are rare

Rewriting in safe languages has challenges: Expensive Talent shortage Risk of introducing bugs

## Much embedded code is intrinsically unsafe

# Some things work to our advantage

- Full control of software

- Break compatibility, drop hybrid mode, simplify ISA

- Very fast tightly coupled memory

- Enables new temporal safety mechanism

### CHERIoT shrinks metadata to 32 bits

| Bounds      | <ul> <li>No guaranteed out-of-bounds range</li> </ul>                                          |  |

|-------------|------------------------------------------------------------------------------------------------|--|

| Sealing     | <ul> <li>Only 3 bits of sealing type</li> <li>Separate code and data sealing spaces</li> </ul> |  |

| Permissions | <ul> <li>12 permissions in 6 bits</li> </ul>                                                   |  |

### And we add things

| Transitive permissions                           | <ul> <li>Permit-load-mutable, deep immutability</li> <li>Permit-load-global, deep no-capture</li> </ul> |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

|                                                  |                                                                                                         |  |  |

| Interrupt control via sentries                   | <ul> <li>Jumping to these enables / disables interrupts</li> </ul>                                      |  |  |

|                                                  |                                                                                                         |  |  |

| Temporal safety via a hardware revocation bitmap | <ul> <li>1 bit per 8 bytes in a separate SRAM bank</li> </ul>                                           |  |  |

### Hardware load barrier adds temporal safety

- Load pointer computes the base address

- Looks up the corresponding revocation bit

- Invalidates the pointer if the memory is freed

```

void *x = malloc(42);

// Print the allocated value:

Debug::log("Allocated: {}", x);

free(x);

// Print the dangling pointer

Debug::log("Use after free: {}", x);

```

Valid bit cleared, *any* attempt to use as a pointer will trap

Allocating compartment: Allocated: 0x80005900 (v:1 0x80005900-0x80005930 l:0x30 o:0x0 p: G RWcgm- -- ---) Allocating compartment: Use after free: 0x80005900 (v:0 0x80005900-0x80005930 l:0x30 o:0x0 p: G RWcgm- -- ---)

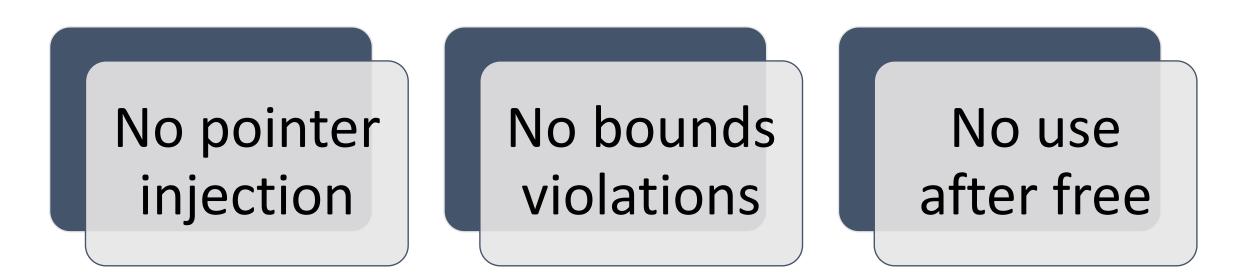

### Baseline security guarantees

The system can assume these for building higherlevel abstractions.

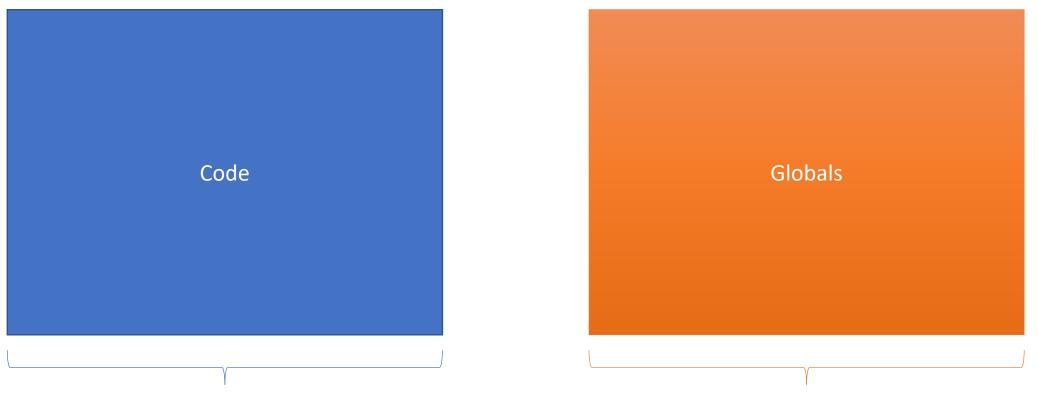

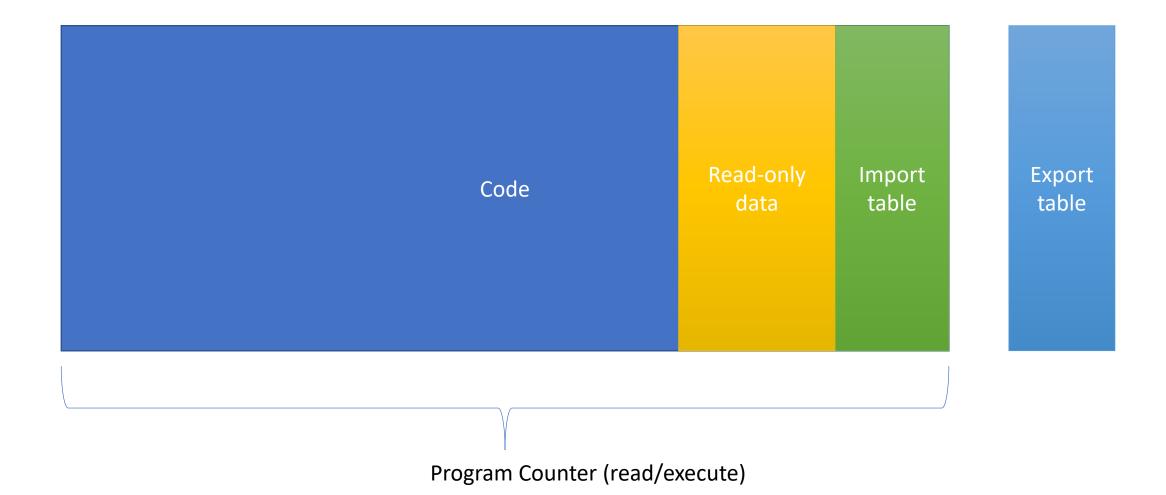

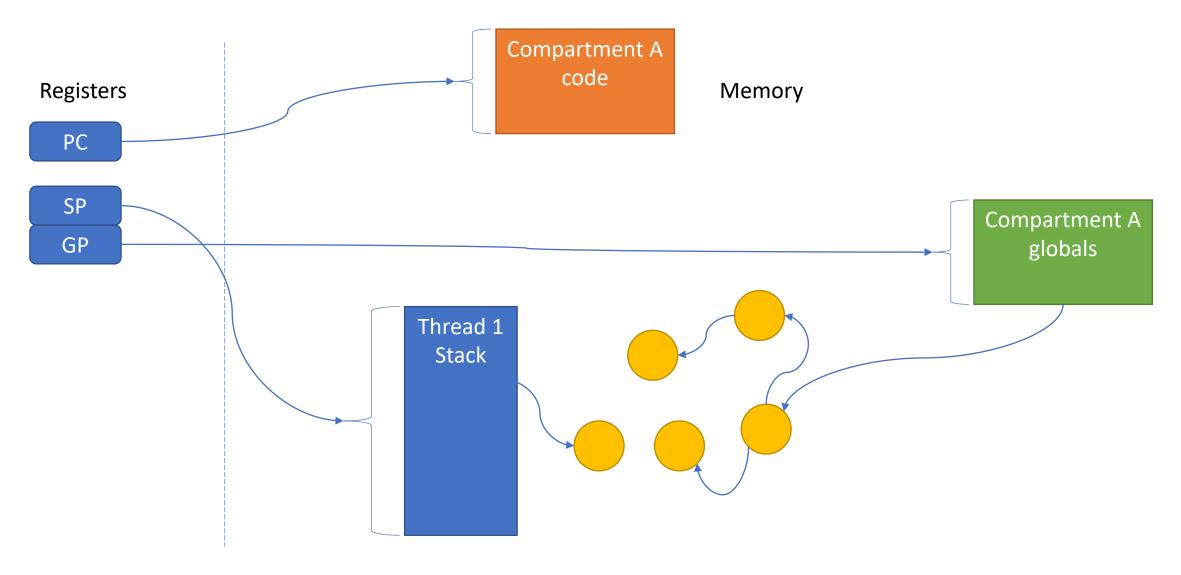

### Compartments are code and data

Program Counter (read/execute)

Global Pointer (read/write/global)

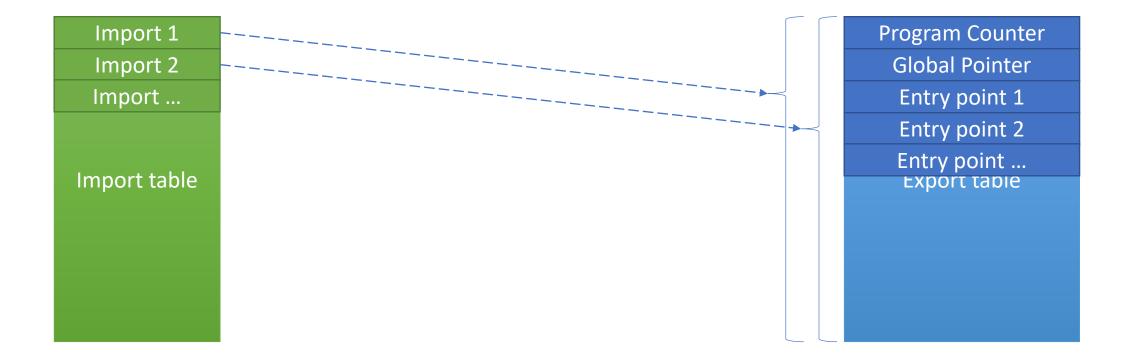

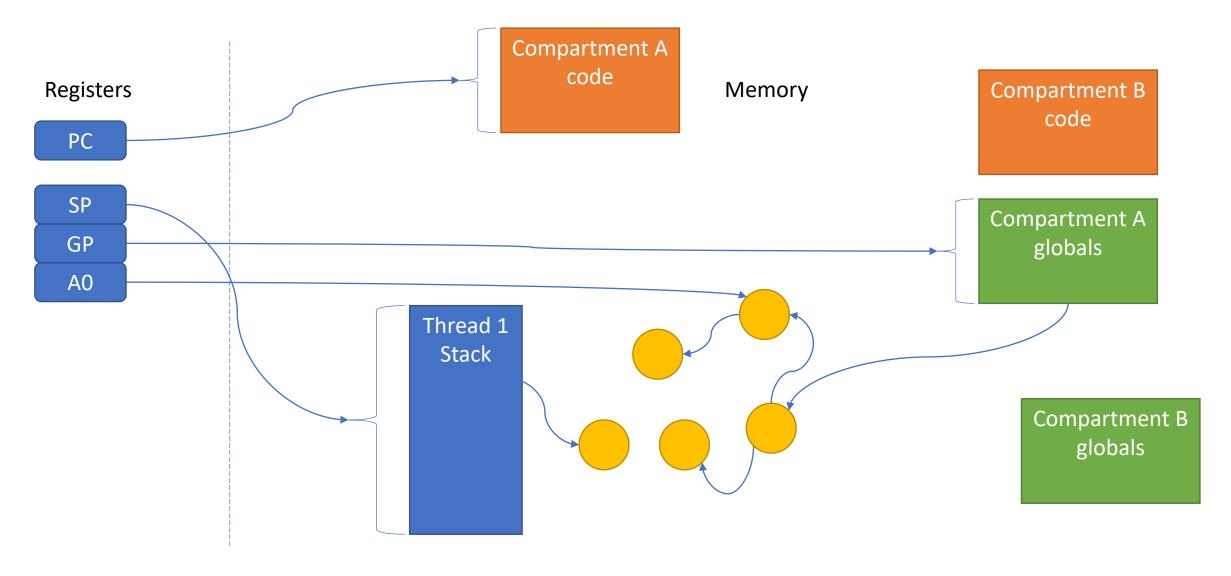

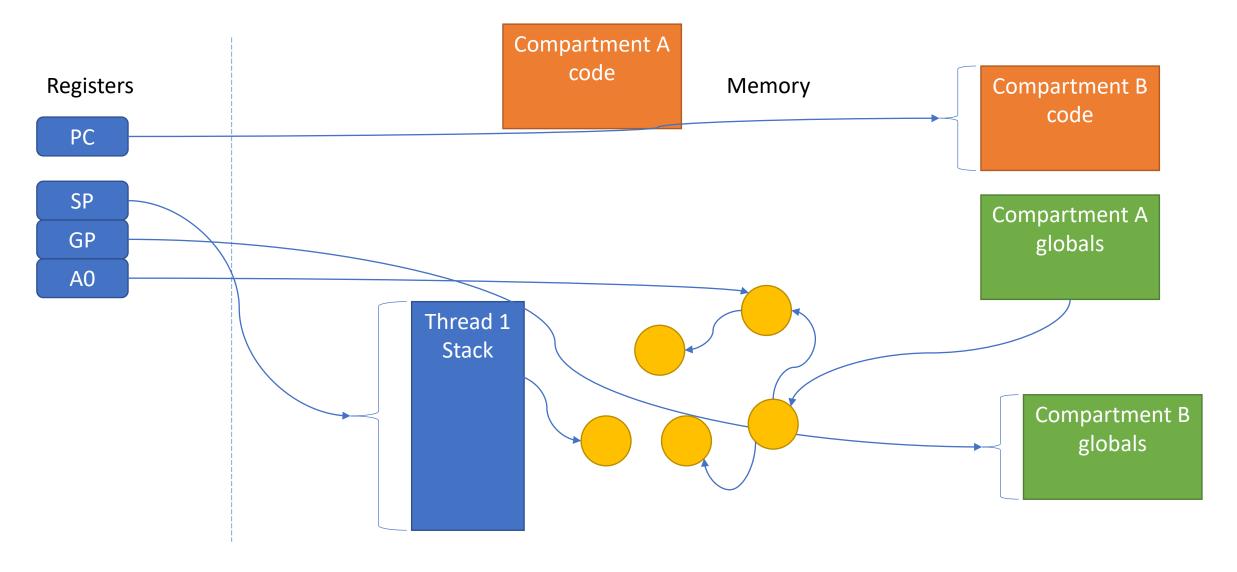

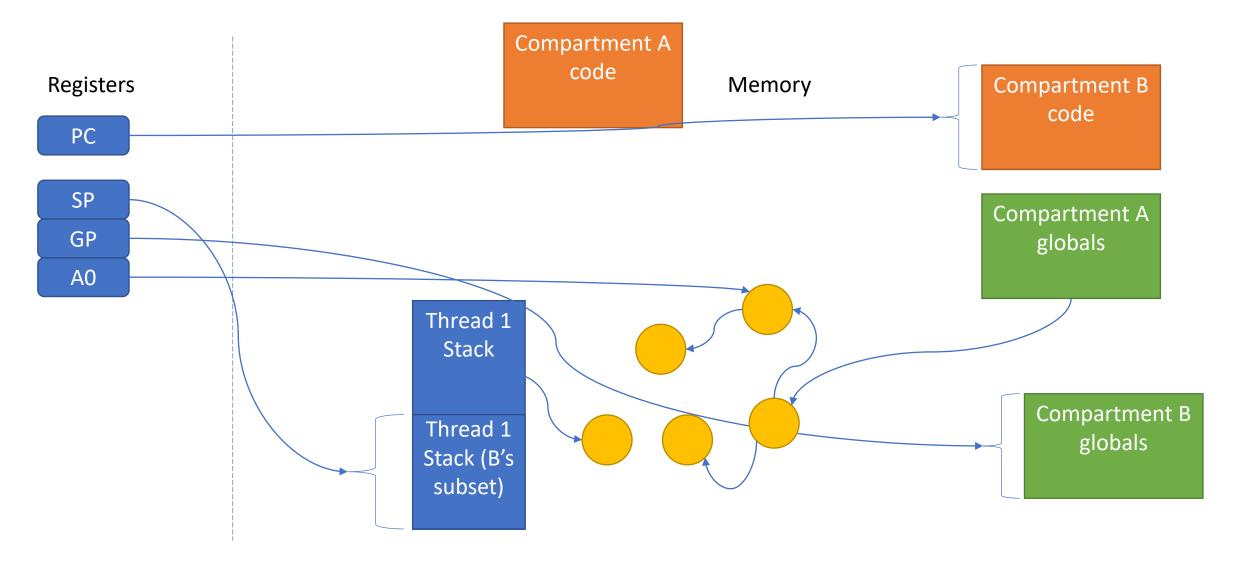

### Compartments are code and data and exports

### Compartments are code and data and exports

### Security guarantees across compartments

### No sharing except via explicit pointer passing

Pointers from the caller may prevent modification or capture

### Trusted (privilegeseparated) components

#### Loader

- Has full access to all memory

- Erases itself after boot

- Not needed if flash can store tags

#### Switcher

- Can see state from multiple threads and compartments

- Has access to a reserved register (and system registers)

- Around 300 instructions

#### Scheduler

- Trusted for availability

- No access to suspended thread state (registers or stack)

#### Memory allocator (optional)

• Sets bounds / revocation state on allocations

### Add compartmentalization to C/C++

// Declaration adds an attribute to indicate

// the compartment containing the implementation

void \_\_attribute\_\_((cheri\_compartment("kv\_store\_sdk")))

publish(char \*key, uint8\_t \*buffer, size\_t size);

// Call site looks like normal C.

- // Compiled to a direct call in compartments build with

- // -cheri-compartment=kv\_store\_sdk

- // Compiled to a cross-domain call in all other cases.

- uint8\_t buffer[BUFFER\_SIZE];

- publish("key\_id", buffer, sizeof(buffer));

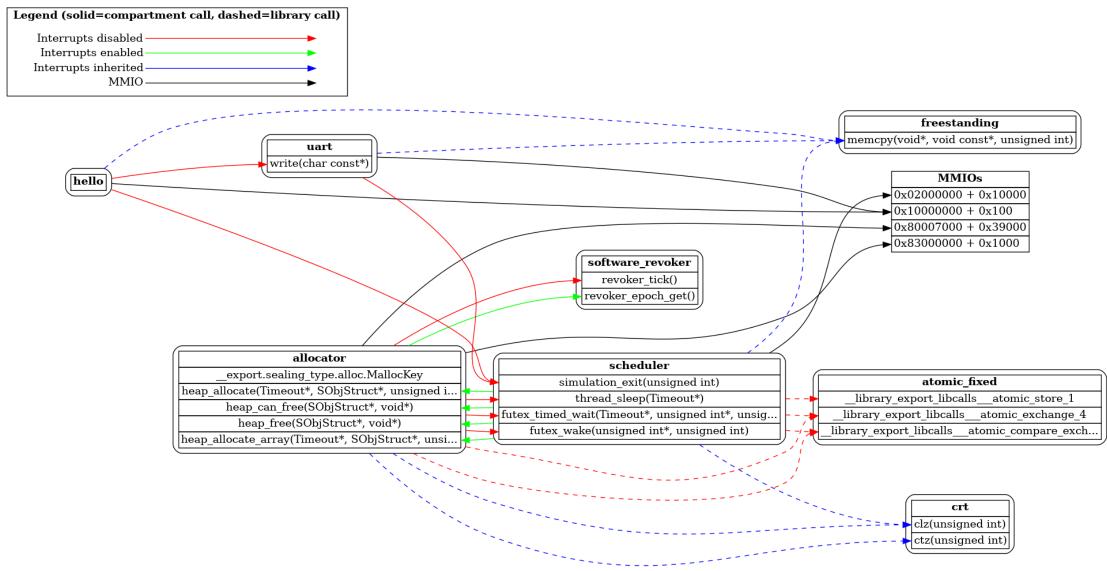

### Linker reports

| _ |                                                                                        |

|---|----------------------------------------------------------------------------------------|

|   | <pre>"compartments": {</pre>                                                           |

|   | "allocator": {                                                                         |

|   | <pre>"code": {     "inputs": [</pre>                                                   |

| / |                                                                                        |

|   | ],<br>"name": "allocator_code",                                                        |

|   | <pre>""""""""""""""""""""""""""""""""""""</pre>                                        |

|   | "sha256": "e882c4ec2585f5f1100f8652b4838dcd77d747ab0918101bee46dd2efb16a4df"           |

|   | <pre>Sila230 . * E882(4E(238313110018032048380C07/07478005181010EE40002E10108401</pre> |

|   | ·····},                                                                                |

| > | "exports": [                                                                           |

|   | ·····],                                                                                |

| > | "imports": [                                                                           |

|   |                                                                                        |

|   | ·····},                                                                                |

| > | "atomic_fixed": {                                                                      |

|   | ····},                                                                                 |

| > | "crt": {                                                                               |

|   | ····},                                                                                 |

| > | <pre>"freestanding": { ···</pre>                                                       |

|   | ····},                                                                                 |

| > | "hello": { ···                                                                         |

|   | },                                                                                     |

| > | ·····scheduler": {···                                                                  |

|   | ····},                                                                                 |

| > | ····"software_revoker": {···                                                           |

|   |                                                                                        |

|   | },<br>"core": {                                                                        |

|   | · core : {                                                                             |

|   | "file": "build/cheriot/cheriot/release/hello_world",                                   |

|   | "final_hash": "97c8b5344a4eb096a77d1a3a0d7397823d2ce677801c82a8a5a1357456ac2ecb"       |

|   |                                                                                        |

### What can we statically audit?

Everything in this talk is open source

https://aka.ms/cheriot-tech-report

The ISA specification: https://github.com/microsoft/cheriot-sail

The reference core: <a href="https://github.com/microsoft/cheriot-ibex">https://github.com/microsoft/cheriot-ibex</a>

The embedded OS:

https://github.com/microsoft/cheriot-rtos

The compiler (cheriot branch):

https://github.com/CTSRD-CHERI/llvm-project/

### Thanks

- UKRI / DSbD / CHERITech

- All prior CHERI work we've built on / inspired us:

- CHERI-RISCV Arch + LLVM

- CompartOS (Almetary)

- CheriOS(Esswood)

- CHERI-RTOS (Xia)

- Sail

- Ibex / ETH Zurich / LowRISC

- ...

### Summary

Fine-grained spatial and temporal memory safety guarantees for C/C++

#### Lightweight compartments

Safe bounded cross-compartment sharing

Strong attestation over compartment structure

Any more questions, please ask in the GitHub Microsoft/CHERIoT-RTOS Discussions! https://github.com/microsoft/cheriot-rtos/discussions/categories/q-a

### Backup

### Most codebases require very few changes

#### Microvium embedded JavaScript interpreter

• No changes

#### TPM reference stack

- No changes for memory safety

- Small changes (<10LoC) for RISC-V

- One line changed to run in a compartment

#### FreeRTOS network stack

- No changes for memory safety

- Annotations for crosscompartment calls

- Explicit sealing and unsealing

- Small changes (~100 LoC) to run without disabling interrupts for mutual exclusion

#### mBedTLS

- No changes for memory safety

- Small changes for compartmentalisation

### Capability format

| 31   |             | 25 | 24 2   | 2 21 | 18  | 17 9 | 8 0 |

|------|-------------|----|--------|------|-----|------|-----|

| R    | p <b>'6</b> |    | otype' | 3    | E'4 | B'9  | T'9 |

| a'32 |             |    |        |      |     |      |     |

- **R** a reserved bit, which is zero in the root capabilities (and hence all tagged capabilities), but may be set if untagged data is loaded into a register. In this case its value must be preserved. This is very important because memory copies are performed with capability load a store instructions in order to preserve the tag on any capabilities present, meaning these instructions must also faithfully copy arbitrary untagged data.

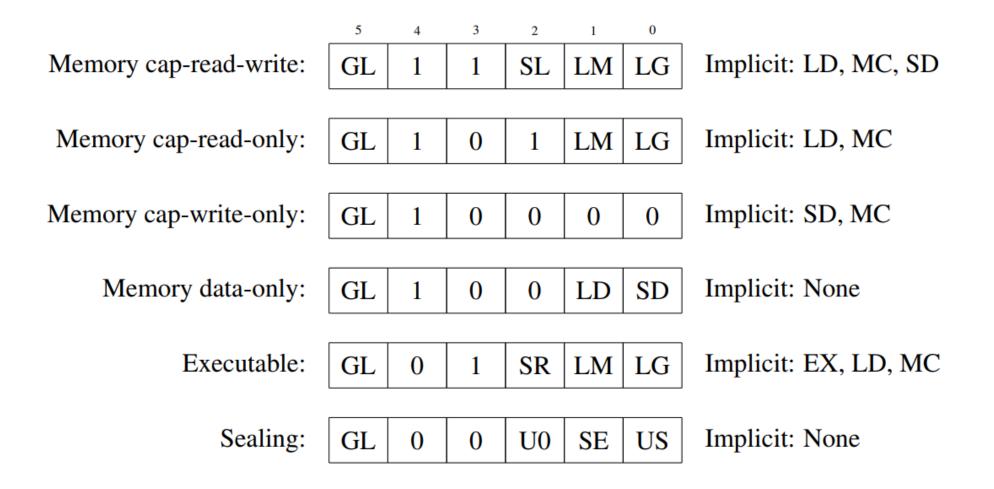

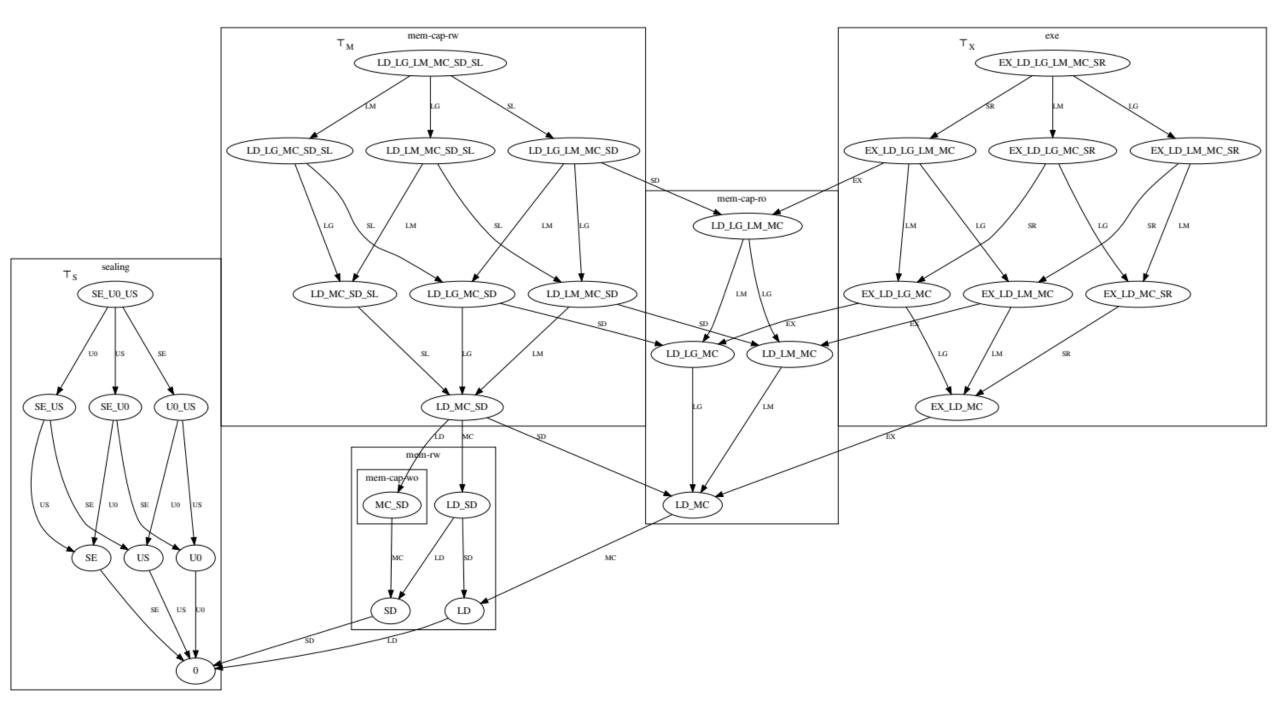

- **p** a 6-bit compressed permissions field (see Section 7.13.1)

- otype a 3-bit 'object type' used for sealing capabilities (see Section 7.13.2)

- E a 4-bit exponent used for the bounds encoding (see Section 7.13.3)

- **B** a 9-bit base used for the bounds encoding (see Section 7.13.3)

- T a 9-bit top used in the bounds encoding (see Section 7.13.3)

- **a** the 32-bit address of the capability

### Permission encoding