## Sample Exam Question Model Answer (Week 23 Tutorial)

## Comments

Pay attention to the number of marks attached to each question, because it is a good guide to the amount of information that the answer should contain. This is particularly relevant here to section (a). For 1 mark, you just need a short, simple answer. For 2 marks you should be making 2 points, etc.

## **Question 1: Model Answer**

- (a). (i) A high-level language, for example Ada, allows us to write a program in a way that is close to the way we think about a problem (1 mark). A low-level language, for example ITM machine language, uses simple instructions that can be directly executed by a CPU (1 mark)

- (ii) A D flipflop is a single bit memory: we can store either 0 or 1 in it (1 mark). A group of D flipflops makes a register, which is an important component within a CPU (1 mark).

- (iii) A sequential circuit is one which has memory or state information, so that its behaviour depends on past as well as present inputs (1 mark). A circuit with no memory, whose output only depends on its present inputs, is called combinational (1 mark). A CPU is an example of a sequential circuit (1 mark).

- (iv) Any three of: the registers are used for storage (1 mark), the ALU is used for calculations (1 mark), the control unit decodes instructions and activates other parts of the CPU (1 mark), the internal data bus is a pathway for data within the CPU (1 mark).

- (b). You are required to design a circuit which, given an input xyz representing a 3 bit binary number n, produces an output abc representing n+1. For example, if the input is 011 (x=0, y=1, z=1), representing n=3, then the output is 100, representing 4. If the input is 111 then the output is 000.

- (i) One mark for each correct output column of this truth table:

| $\boldsymbol{x}$ | y | z | a | b | c |

|------------------|---|---|---|---|---|

| 0                | 0 | 0 | 0 | 0 | 1 |

| 0                | 0 | 1 | 0 | 1 | 0 |

| 0                | 1 | 0 | 0 | 1 | 1 |

| 0                | 1 | 1 | 1 | 0 | 0 |

| 1                | 0 | 0 | 1 | 0 | 1 |

| 1                | 0 | 1 | 1 | 1 | 0 |

| 1                | 1 | 0 | 1 | 1 | 1 |

| 1                | 1 | 1 | 0 | 0 | 0 |

## CS1Q Computer Systems

(ii) One mark for each correct Karnaugh map:

|                  |                | a              |   |                |                |                | b              |   |   |   |                |                | c              |   |                |

|------------------|----------------|----------------|---|----------------|----------------|----------------|----------------|---|---|---|----------------|----------------|----------------|---|----------------|

|                  |                |                |   | $\overline{y}$ |                |                | y              |   |   |   |                | $\overline{y}$ | y              | y | $\overline{y}$ |

| $\overline{x}$   | 0              | 0              | 1 | 0              | $\overline{x}$ | 0              | 1              | 0 | 1 |   | $\overline{x}$ | 1              | 1              | 0 | 0              |

| $\boldsymbol{x}$ | 1              | 1              | 0 | 1              | x              | 0              | 1              | 0 | 1 |   |                | 1              |                |   | 0              |

|                  | $\overline{z}$ | $\overline{z}$ | z | z              |                | $\overline{z}$ | $\overline{z}$ | z | z | • |                | $\overline{z}$ | $\overline{z}$ | z | $\overline{z}$ |

(iii) One mark for each formula.

$$a = x\overline{z} + x\overline{y} + \overline{x}yz$$

$$b = y\overline{z} + \overline{y}z$$

$$c = \overline{z}$$

Minor variations are also correct, e.g.  $a = x(\overline{y} + \overline{z}) + \overline{x}yz$ ,  $b = y \oplus z$ .

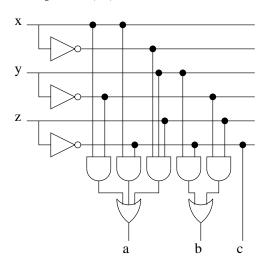

(iv) One mark for each correct part: a, b, c.

(v) Here we've used 10 gates to build a circuit which adds 1 to a 3 bit number (1 mark). If we used a 3 bit adder to do this, we would have 3 single bit full adders. Each full adder consists of 2 half adders and one more gate. Each half adder consists of 2 gates. So the 3 bit adder uses 15 gates (2 marks for calculation). In other words, this specialised circuit for adding 1 is more efficient (in a certain sense).